# UNIVERSITÀ DEGLI STUDI DI PALERMO

### Corso di Dottorato in ENERGIA E TECNOLOGIE DELL'INFORMAZIONE

Dipartimento di Energia, ingegneria dell'Informazione e modelli Matematici (DEIM) Settore scientifico disciplinare: ING-INF/01

# ELECTRICAL AND OPTICAL PROPERTIES OF GRAPHENE FIELD-EFFECT TRANSISTORS (GFETs) FABRICATED ON **SAPPHIRE**

IL DOTTORE

Marco Angelo Giambra

IL COORDINATORE Prof.ssa M. S. Mongiovì

Morria Stelle Moupist.

**I TUTORS**

Dr. Ing. Salvatore Stivala

Prof. Ing. Alessandro Busacca

Prof. Ing. Enrico Calandra

CICLO XXIX ANNO CONSEGUIMENTO TITOLO 2017

# Università degli Studi di Palermo

Dipartimento di Energia, ingegneria dell'Informazione e modelli Matematici

# Corso di Dottorato in ENERGIA E TECNOLOGIE DELL'INFORMAZIONE Curriculum

Tecnologie dell'Informazione e Scienze Applicate

Ciclo XXIX

# Electrical and optical properties of graphene fieldeffect transistors (GFETs) fabricated on sapphire

#### Ph.D. thesis

| PH.D. STUDENT | Marco Angelo Giambra                                                      |

|---------------|---------------------------------------------------------------------------|

| TUTORs        | Dr. Salvatore Stivala, Prof. Alessandro Busacca,<br>Prof. Enrico Calandra |

# **Abstract**

Graphene, a monolayer of carbon atoms arranged in a honeycomb lattice, is still one of the most investigated fields of research in condensed matter physics since its discovery in 2004 [1], [2]. The reasons for its amazing success are the unique electronic, optical, mechanical and thermal properties such as its extremely high charge carrier motility, the quantum Hall effect observed at room temperature and its flexibility, as well as mechanical strength. Among the various potential application fields, high frequency electronics and photodetection represent two of the most promising ones. Graphene field effect transistors (GFETs) for high frequency applications have been already fabricated [3] exploiting the electronic transport properties of the graphene. GFETs have rapidly developed and are now considered for post-silicon Electronics. However, different techniques have been developed to grow graphene to large scale production, such as CVD graphene or graphitization of silicon carbide. Promising results exploiting such techniques have been reached inducing the research to deeply invest on this field, although the quality of the obtained graphene is not equal to that obtained by mechanical exfoliation in terms of mobility [4]. Fabrication of high-performances GFETs is an important challenge, since a conventional device-fabrication process can damage the graphene lattice, or introduce excessive parasitic capacitance

or series resistance, thus resulting in degraded electronic performances [5]. The high graphene carriers mobility is not the only important feature in graphene-based devices, in fact, concerning high frequency transistors, the possibility to fabricate devices with extremely short channels is highly desired, since this could allow GFETs to be scaled to shorter channel lengths and higher speeds without encountering short-channel effects which restrict the performance of existing devices [3].

On the other hand, graphene absorbs visible in a wide frequency range with an almost constant absorption rate of 2.3% [6]. Photodetectors made of graphene operating at 10 Gbps have already been realized [7]. Combining electronic and optical signal processing is highly desirable, since higher processing speed at less power consumption is possible. A strong nonlinear electromagnetic response of graphene due to the linear dispersion relation has been proposed [8], [9] and experimentally verified [10]. This paves the way to a new field of potential applications for graphene: nonlinear signal operations such as modulators, demodulators or frequency converters (mixers). These components are needed, for instance, in telecommunication engineering.

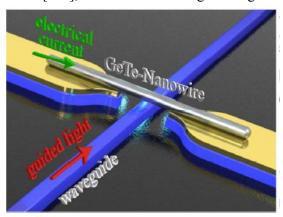

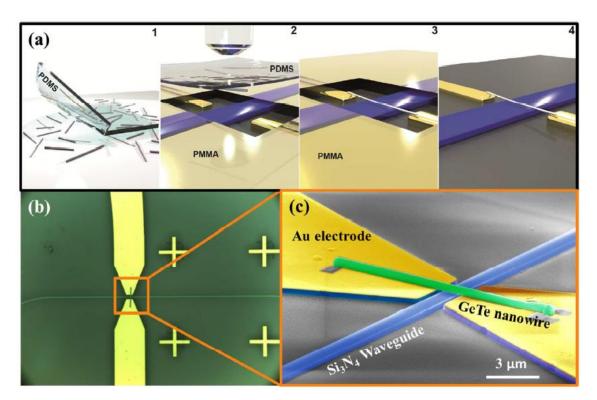

Aim of my PhD work has been the design, fabrication and characterization of GFETs for both high frequency applications and photodetection. The limits of GFETs performances are due to several effects, such as contact resistance, degradation of the mobility and hysteresis. In the work described in this thesis, great effort has been made to minimize these effects in order fully exploit graphene properties. The work has been carried out within the *Laboratorio di Elettronica delle Microonde* (LEM) of the University of Palermo (Italy) and the *Institute of Technology* (INT) of *Karlsruher Institut für Technologie* (KIT, Germany). Devices manufacturing have been carried out at the INT with the aim to fabricate different families of transistors with several device structures. The influence of the layout on microwave performances of Graphene Field Effect Transistors has been investigated finding an important role of the device structure. This work has been associated with a preliminary optical characterization of the devices under test. Finally, a subsequent device family has been fabricated with the aim to analyze the role of the gate dielectric on RF/Opto fields. A supplementary work has been made on GFETs trying to exploit a novel geometry to improve their high frequency performances and on phase change material employed for mixed mode in nanophotonic circuits aimed to non-volatile memory application.

# Acknowledgements

This thesis will be stored in my university and of course in my parent's house and my friends' house, so for this reason I decided to make an Italian version for my acknowledgements in order to let them understand how much importance they had on my journey...

Usually, make the acknowledgements, has never been something simple, especially when you have to rethink about such intense and busy period, full of special moments, difficulties, where there have been people who just came to see, people who asked only for a passage but they stopped during the course and special people, instead, who has been enriching every moment of my life.

So, starting from this, I can only begin to thank those who have supported both didactically and morally in these three years of PhD. So a special thanks goes to my professors Alessandro Busacca, Salvatore Stivala and Enrico Calandra. They have been and they are special professors, for how they have led me, accompanied and followed during this long journey, not just as teachers, but much more. The confidence they gave me has been important and sincere pushing me to do the utmost and above all to believe in me following all their minutious tips to try to always strive up, not content myself and to assert my thinking, so Thanks my professors.

The atmosphere lived in the lab in Palermo has always been special thanks to my colleagues and palermitan friends. I talk in particular about Dr. Riccardo Pernice, Dr. Antonio Benfante, Dr. Gabriele Adamo, Dr. Antonino Parisi, Dr. Saverio Guarino and Professor Alfonso Cino. I have to thank Dr. Riccardo Pernice for his patience but at the same time for his sweetness in following me in drawing up my PhD thesis. I would not forget anyone, but it will happen, so to limit the damage, since DEIM has been a second home, I would like to thank all the professors, researchers and PhD students in my department who have always given me a smile for my journey which has always been well accepted. Since my PhD course in Palermo can not only be placed at DEIM, special thanks should be given to Professor Calandra and his family, Mrs. Calandra, Alberto who welcomed me all those days, happy but also difficult, always with the smile, giving me strength and making me understand how much importance the family can have in our lives.

Moving from Italy to Germany, I would also like to thank my relator at KIT Dr. Romain Danneau, Dr. Prof. Wolfram Hans Peter Pernice and Prof. Ralph Krupke. Their guide has been very important in the development of my research project and on the writing of my PhD thesis. I also thank my colleagues from many parts of the world, such as Dr. Patrick Rath, Dr. Matthias Stegmaier, Dr. Wladislaw Hartmann, Anna Ovvyan, Dr. Simone Ferrari, Dr. Christian Benz, Dr.

Sa Svetlana, Dr. Jens Mohrmann, Preeti Pandey, Rainer Kraft, Rava, Renjuun Du, Geethu Balachandran, Muraleetharan Boopathi, Renjun Du, Saumya Gupta, Nico Gruhler, Nicolas Kurz, Joachim Schönle, Nicolai Walter and Fan Wu.

Germany for me was not just the PhD ... indeed, I remember when I arrived there and I did not know a German word ... all new, the scents, the flavors, the climate ... but above all, the people ... I was there before the beginning of this Doctoral course, in order to make experience, to test myself. If I managed to "survive," I have to thank special people. I refer to my colleagues at "La Pizza". They welcomed me, they made me feel at home. They helped me, they made me understand that I could make it; Tighten your teeth, wash dishes, tables and bake pizzas. The jokes and affection of Gino Pinto and Sino Pendola, the sweetness of Herman, the mythical Ciccio Meli who also gave me a bed and a room to sleep, like Gino who I thank so much. If I was able to stay, there is also thanks to you and I am grateful to you.

Far away only physically, but always with me, in my heart, there was my family. Once again I have not been next to you in periods which had not been easy for you and for me ... but you are and you will always be with me. Thanks Mom Graziella, Daddy Maurizio, Luca, Roberta and Andrea. It was always an immense joy to return to Sicily at our home. You have always been a column in my life ... my mom who has always helped me to solve any problem, even at 2500 kilometers far away and Dad who was worried I was so far away ... Dad, believe me, this was a way to prove that I'm not weak, but I'm as strong as you ... that I can take my responsibilities, and that I want to learn more and more than I can in order to be better in any field so that one day you can be proud of me ... proud of your son who knows how much you've done for him and he like you, wants to build his future, be precise and efficient, just as you've always been. Thank you Dad and Mom ... Thank you for being always close to me.

I knew that in this life, it is possible to meet only a few real friends, and I think that I found some of them without any doubt. They gave me so much strength and happiness. I'm talking about special people who I hope they will be part always of my life ever. I talk about Alessio Galante, Flaviano Brunacci, Angelo Capuana, Ciccio Bob, Peppe Modica, Massimo Galante and Giovanni Sciandra. I can not dwell on each of you because I would write a Bukowskian poem, but you know how important you are for me. A hug, a glance and everything is clear. I love you my friends.

I thank Rosalba Bertorotta, Giuseppe di Paola and Alessia who supported me, welcomed and make me feel always at home.

Halfway through this path, something has shaken my life ... something great, something intense ... I thought that something like this could not happen again, but it happened, with a great strength and at the same time a great sweetness. Fate let us to meet each other, that I have the opportunity

to live each other and the more time passes and the more you make me fall in love with you ... in the most beautiful moments but above all in the toughest moments when I no longer knew how to do, when I felt lost ... you've always been there with me ... you took me by the hand and you gave me that strength I needed to get up and start again stronger than before. You've been always around me; you've come to live in Germany with me... just to make me feel good. All this is not something trivial, indeed, something wonderful because that's what you did ... Serena made my life wonderful ... just because you were here next to me ... so this thesis, this energy, this experience Is dedicated to you ... Thank you love ...

Fare i ringraziamenti non è mai stato qualcosa di semplice, soprattutto quando si deve ripensare a degli anni così intensi e ricchi di momenti speciali, difficoltà, gente che è passata solo a vedere, gente che ha chiesto un passaggio ma si è fermata durante il percorso e gente speciale, invece, che è rimasta arricchendo ogni momento della mia vita.

Quindi, partendo da questo, non posso che non iniziare nel ringraziare coloro che mi hanno supportato sia didatticamente che moralmente in questi tre anni di dottorato. Quindi un ringraziamento speciale va ai miei professori Alessandro Busacca, Salvatore Stivala e Enrico Calandra. Sono stati e sono dei professori speciali, per come mi hanno guidato, accompagnato e seguito durante questo lungo percorso, non solo come docenti, ma molto di più. La fiducia datami è stata importante e sincera, armi che mi hanno spinto a dare il massimo e soprattutto nel credere in me a seguito di tutti i minuziosi consigli per cercare di tendere sempre in alto, non accontentarmi mai e far valere il mio pensiero, quindi grazie professori.

Il clima vissuto in laboratorio a Palermo è sempre stato speciale anche grazie ai miei colleghi e amici Palermitani. Parlo in particolare del Dr. Riccardo Pernice, il Dr. Antonio Benfante, il Dr. Gabriele Adamo, il Dr. Antonino Parisi, il Dr. Saverio Guarino e il Professore Alfonso Cino. Al Dr. Riccardo Pernice devo un ringraziamento particolare dovuto alla sua pazienza ma, allo stesso tempo alla sua dolcezza nell'avermi seguito nella stesura della mia tesi di Dottorato. Vorrei non dimenticare nessuno, ma accadrà, quindi per limitare i danni, visto che ormai il DEIM era una seconda casa, ringrazierei tutti i professori, i ricercatori e i dottorandi del mio dipartimento che mi hanno concesso sempre un sorriso o un in bocca al lupo per il mio percorso che è stato sempre ben accetto. Visto che il mio percorso di dottorato a Palermo non si può solamente collocare al DEIM, un ringraziamento speciale va fatto al Professore Calandra e alla sua famiglia, Signora Calandra, Alberto, i quali mi hanno accolto in tutti quei giorni, felici ma altri anche difficili, sempre col sorriso, dandomi forza e facendomi capire quanta importanza può avere la famiglia nella nostra vita.

Passando invece dall'Italia alla Germania, un ringraziamento importante va fatto al mio relatore presso al KIT Dr. Romain Danneau, al Dr. Prof. Wolfram Hans Peter Pernice e al Prof. Ralph Krupke. La loro guida è stata importantissima nello sviluppo del mio progetto di ricerca e nella stesura della mia tesi di dottorato. ringrazio anche i miei colleghi provenienti da tante parti del mondo, quali il Dr. Patrick Rath, Dr. Matthias Stegmaier, Dr. Wladislaw Hartmann, Anna Ovvyan, Dr. Simone Ferrari, Dr. Christian Benz, Dr. Sa Svetlana, Dr. Jens Mohrmann, Preeti Pandey, Rainer Kraft, Rava, Renjuun Du, Geethu Balachandran, Muraleetharan Boopathi, Renjun Du, Saumya Gupta, Dr. Nico Gruhler, Nicolas Kurz, Joachim Schönle, Nicolai Walter, and Fan Wu.

La Germania per me non è stata solo dottorato...anzi, ricordo quando arrivai lì e non sapevo una parola di tedesco...tutto nuovo, i profumi, i sapori, il clima...ma soprattutto la gente...ero lì da prima dell'inizio di questo percorso di dottorato, per fare esperienza, per mettermi alla prova. Se sono riuscito a "sopravvivere" lo devo a delle persone speciali. Mi riferisco ai miei colleghi della Pizzeria "La Pizza". Loro mi hanno accolto, e anche se per poco, mi hanno fatto sentire a casa. Mi hanno aiutato, mi hanno fatto capire che ce la potevo fare; stringere i denti, lavare piatti, tavoli e infornare pizze sentendoli sempre attorno a me. Le battute e l'affetto di Gino Pinto e Sino Pendola, la dolcezza di Herman (che mi sorride da lassù), il mitico Ciccio Meli che mi ha dato pure un letto e una stanza dove dormire, come Gino che ringrazio tanto. Se sono riuscito a star lì è anche grazie a voi ed io ve ne sono grato.

Lontana solo fisicamente, ma sempre con me, nel mio cuore, c'è stata la mia famiglia. Ancora una volta non sono stato lì accanto a voi in momenti per voi e per me non facili...ma siete e sarete sempre con me. Grazie Mamma Graziella, Papà Maurizio, Luca, Roberta e Andrea. Era sempre una gioia immensa tornare in Sicilia a casa nostra. Siete sempre stati una colonna nella mia vita...la mamma che mi ha sempre aiutato a risolvere qualsiasi problema anche a 2500 chilometri e Papà a cui mancavo e mi mancava tanto, che si preoccupava che fossi così distante...papa, credimi, anche questo era un modo per dimostrarti che non sono debole, che sono forte come te...che so prendermi le mie responsabilità, e che voglio imparare più che posso e diventare sempre più bravo, in qualsiasi ambito, così che un giorno tu possa essere fiero di me...fiero di tuo figlio che sa quanto hai fatto per lui e lui come te, vuole costruire il suo futuro, essere preciso ed efficiente, proprio come sei sempre stato tu. Grazie Papà e Mamma...Grazie di essermi stato sempre vicino.

Sapevo che in questa vita si incontrano solo pochi veri amici, ed io penso che alcuni li ho trovati e non ho nessun dubbio, loro mi hanno dato tanta forza e felicità. Sto parlando di persone speciali che spero faranno parte della mia vita sempre. Parlo Di Alessio Galante, Flaviano Brunacci, Angelo Capuana, Ciccio Bob, Peppe Modica, Massimo Galante e Giovanni Sciandra. Non posso

soffermarmi su ognuno di voi perché scriverei poemi, magari Bukowskiani, ma voi sapete quanto siete importanti per me. Un abbraccio, un colpo d'occhio e tutto è chiaro. Vi voglio bene amici miei.

Ringrazio Rosalba Bertorotta, Giuseppe di Paola e Alessia che mi hanno sostenuto, accolto e fatto sempre sentire a casa.

A metà di questo percorso, qualcosa ha scosso la mia vita...qualcosa di grande, qualcosa di intenso...Io pensavo che non poteva più succedere qualcosa del genere, ma è accaduto, con una forza e allo stesso tempo una dolcezza immensa. Il destino ha fatto sì che ti conoscessi, che avessi l'opportunità di viverti e più il tempo passa e più riesci a farmi innamorare di te...nei momenti più belli ma soprattutto nei momenti più difficili, quando non sapevo più come fare, quando mi sentivo perduto...tu ci sei sempre stata...mi hai preso per mano e mi hai dato quella forza che mi serviva per alzarmi su e ricominciare ancora più forte di prima. Sei stata presente, sei venuta pure a vivere in Germania con me, pur di starmi vicino..pur di farmi star bene. Tutto questo non è qualcosa di banale, anzi, qualcosa di meraviglioso perché è questo che hai fatto...Serena mi hai reso la vita meravigliosa...solo perché ci sei tu qui accanto a me...e quindi questo lavoro di tesi, questa energia, questa esperienza è dedicata a te...Grazie amore...

# **Contents**

| Abs | tract                                       |                                                                       | ii |

|-----|---------------------------------------------|-----------------------------------------------------------------------|----|

| Ack | nowledge                                    | ements                                                                | iv |

| 1.  | Graphe                                      | ne properties                                                         | 1  |

| 1.1 | Band structure                              |                                                                       |    |

| 1.2 | Graph                                       | ene electronic properties                                             | 3  |

| 1.3 | 3 Graphene optical properties               |                                                                       |    |

|     | 3.1.1                                       | Photodetection mechanisms                                             | 4  |

| 1.4 | Graph                                       | ene growth techniques                                                 | 7  |

| 2.  | Graphene-based devices                      |                                                                       |    |

| 2.1 | Graphene field effect transistors (GFETs)12 |                                                                       |    |

| 2.2 | Hysteresis in graphene-based devices        |                                                                       |    |

| 2.3 | Contact resistance                          |                                                                       |    |

| 2.4 | State of art of GFETs                       |                                                                       |    |

| 2.5 | State of art graphene-based photodetectors  |                                                                       |    |

| 3.  | Experimental activities                     |                                                                       | 19 |

| 3.1 | Substrate19                                 |                                                                       | 19 |

| 3.2 | Gate dielectric                             |                                                                       |    |

| 3.3 | Fabrication techniques21                    |                                                                       |    |

| 3.4 | 4 M4 Device                                 |                                                                       | 28 |

|     | 3.1.2                                       | Design                                                                | 28 |

|     | 3.1.3                                       | Layout influence on GFETs microwave performances                      | 28 |

|     | 3.1.4                                       | DC and RF characterization                                            | 33 |

|     | 3.1.5                                       | Optical measurements                                                  | 35 |

| 3.5 | M7 De                                       | evice                                                                 | 36 |

|     | 3.1.6                                       | Design                                                                | 36 |

|     | 3.1.7                                       | A comparison of different thin oxide films in GFETs performances      | 37 |

|     | 3.1.8                                       | Photodetection in graphene-based transistors for telecom applications | 41 |

| 3.6 | Supple                                      | ementary works                                                        | 44 |

|     | 3.1.9                                       | GFETs exploiting double-clamped geometry                              | 44 |

|     | 3.1.10                                      | Mixed-mode operation of hybrid phase change nanophotonic circuits     | 47 |

| 4   | Conclus                                     | ions                                                                  | 50 |

| A.    | Appendix                  | K                                        | 51 |  |

|-------|---------------------------|------------------------------------------|----|--|

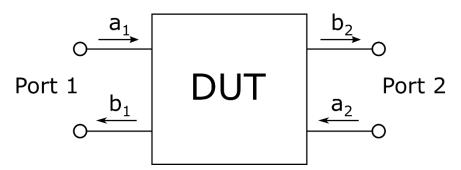

| A.1   | Scatteri                  | ng and admittance parameters             | 51 |  |

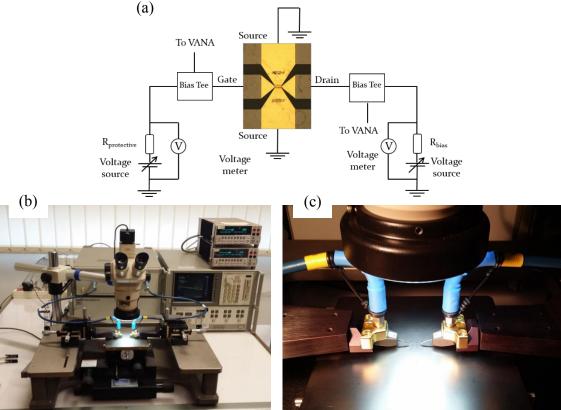

| A.2   | Setup a                   | Setup at LEM                             |    |  |

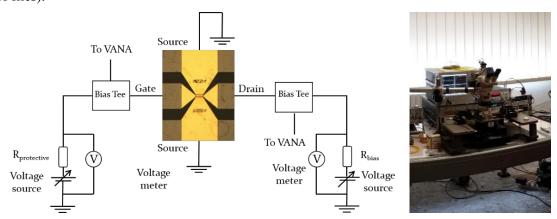

|       | A.2.1                     | DC/RF set-up #1                          | 52 |  |

|       | A.2.2                     | DC/RF set-up #2                          | 54 |  |

|       | A.2.3                     | VANA calibration                         | 55 |  |

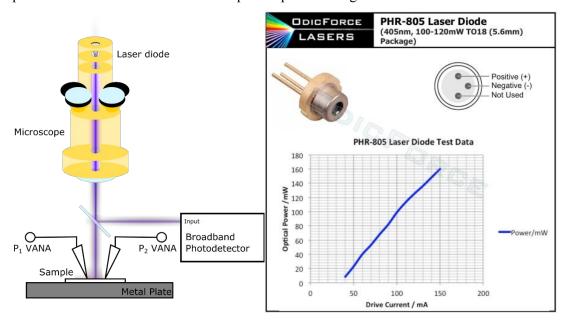

|       | A.2.4                     | Optical set-ups                          | 56 |  |

| A.3   | Set up a                  | up at KIT60                              |    |  |

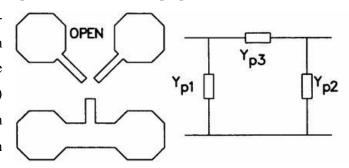

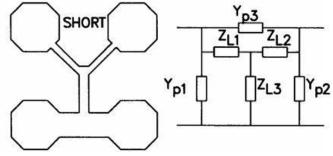

| A.4   | 4 De-embedding techniques |                                          |    |  |

|       | A.4.1                     | Y-parameters based de-embedding approach | 62 |  |

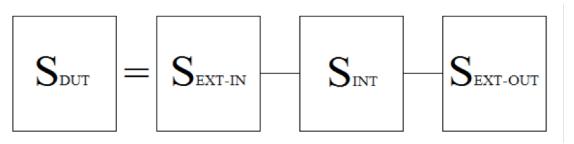

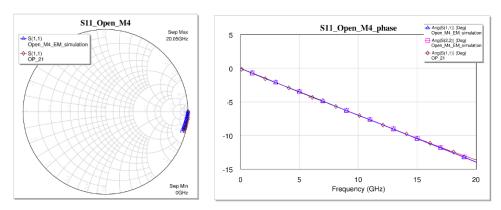

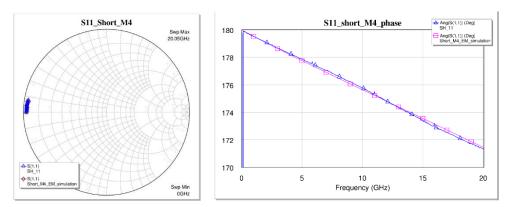

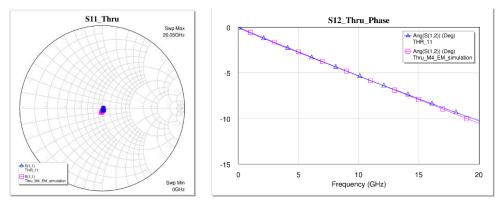

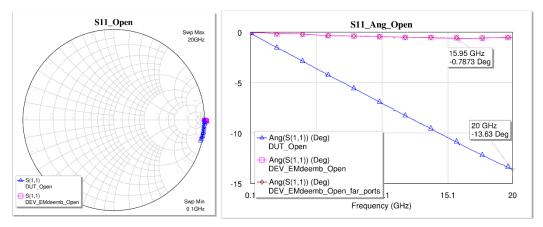

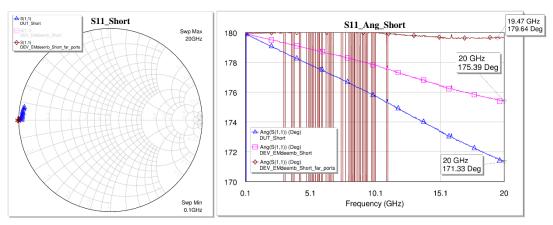

|       | A.4.2                     | Electromagnetic De-embedding             | 63 |  |

| Refe  | rences                    |                                          | 68 |  |

| B: Li | st of publi               | ications                                 | 74 |  |

| B.1 J | 3.1 Journal papers        |                                          |    |  |

| B.2 ( | 3.2 Conference papers     |                                          |    |  |

|       |                           |                                          |    |  |

### **CHAPTER 1**

# 1. Graphene properties

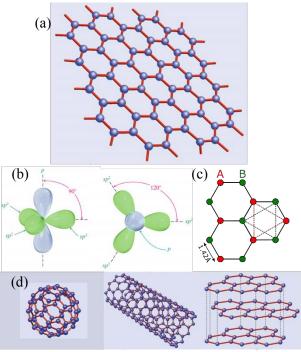

The properties of graphene derive from its crystallographic structure and its 2D nature. It is a single two-dimensional layer of sp<sup>2</sup> hybridized carbon atoms bound in a hexagonal lattice structure (Fig. 1.1(a)). Concerning the orbital planes [11], in the xy-direction (in-plane) the carbon

Fig. 1.1: a) Graphene, a honeycomb lattice of carbon atoms, b) side view and top view of the sp² hybridized carbon, c) lattice structure of graphene obtained by the two interpenetrating triangular lattices, d) graphene allotropes.

Sources: adapted from [11]–[13]

atoms form σ-bonds, responsible for the mechanical strength of graphene, with an orbital angle of 120°. In the z-direction (outof-plane) orbitals form weaker and completely delocalized bonds (i.e.  $\pi$ bonds), responsible for the electronic transport properties of graphene (Fig. 1.1(b)). The honeycomb lattice can be considered as interpenetrations of two triangular sublattices [12], [13] (red and green triangles with dotted lines in Fig. 1.1(c)) where each center is defined by the A (red dots) and B (green dots) with carboncarbon distance of ≈1.42 Å. Great interest has been paid to understand the electronic properties of such material since it is the building block of the different allotropes

[12] shown in Fig. 1.1(d): fullerenes, the 0D allotrope, where some hexagons in the graphene sheet, are replaced by pentagons[14], carbon nanotubes, the 1D allotrope, rolled up graphene sheets[15], and graphite, the 3D allotrope, a stacking of graphene sheets[2] by weak van-der-Waals bonds.

#### 1.1 Band structure

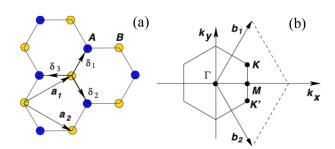

As preliminary described, graphene can be studied as a particular triangular Bravais lattice with a basis of two atoms per unit cell [12], [13] and a tight-binding approximation has been used to describe graphene energy dispersion [12], [16]. Graphene honeycomb lattice and its Brillouin zone are depicted in

Fig. 1.2: a) Graphene honeycomb lattice as an interpenetration of two triangular sublattices, b) related Brillouin zone. Source: adopted by [12].

Fig. 1.2. By looking at Fig. 1.2(a), a real and a reciprocal lattice can be considered with the following lattice vectors:

$$\dot{a}_1 = \frac{a}{2}(3,\sqrt{3}), \ \dot{a}_2 = \frac{a}{2}(3,-\sqrt{3})$$

(1)

$$\dot{b_1} = \frac{2\pi}{3a} (1, \sqrt{3}), \ \dot{b_2} = \frac{2\pi}{3a} (1, -\sqrt{3})$$

(2)

where a is the carbon-carbon distance. From the associated Brillouin zone depicted in Fig. 1.2(b), it is possible to introduce the two important points K and K' named Dirac points, placed at the

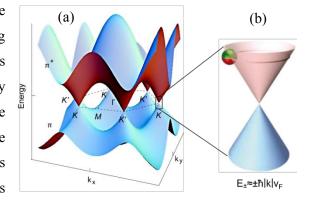

corners of the graphene Brillouin zone. The graphene band structure obtained by solving its associated Hamiltonian [17], [18] is depicted in Fig. 1.3. Thanks to the similarity of its associated Hamiltonian, the particles are quantum mechanically described by the massless Dirac equation [12]. The Dirac cones are located at the K and K' points. In this particular case, the Fermi velocity used in the calculations does not depend on the energy or momentum [12], [13]. In addition, by looking

Fig. 1.3: a) Energy dispersion plot of graphene. The conduction and valance bands touch at the six Dirac points (K, K'). For low energy, the dispersion diagram can be considered as linear (b). Source: adopted from [12]

at the energy dispersion plot, the conduction and valence band touch in the Dirac points (at the six corners of the Brillouin zone) (Fig. 1.3(a)). For low energy (|E| < 1eV) the electron energy is linearly dependent on the wave vector, thus assuming the shape of a cone (Fig. 1.3(b)) [12].

### 1.2 Graphene electronic properties

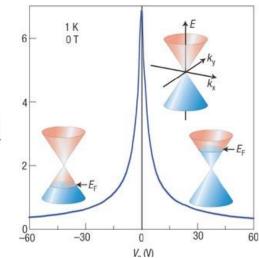

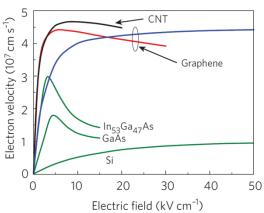

The ability to modify the electronic properties of a material by varying the carrier concentrations, by means of an external electric field, is the key task in electronics. Great interest has been paid

concerning electronic transport in graphene, thanks to its very high carrier concentration and mobility [2]. Ambipolar field effect has been already proved in graphene [1], [2], [19]. In particular, it has been demonstrated that charge carriers can be tuned between electrons and holes in concentrations n as high as  $10^{13} \text{ cm}^{-2}$ with mobilities μ 15,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> under ambient conditions [2]. The extremely high mobility values are always related to large-area gapless graphene, which can be compared by the conventional semiconductor where the electron mobility

Fig. 1.4: Resistivity in graphene by applying an external electric field. A positive gate voltage provokes a ndoping of the material and vice versa by moving the Fermi energy level  $(E_F)$  as shown in the inset. Source: adopted from [2].

decreases as the bandgap increase [3]. Charge carriers can be both electrons or holes and additionally, by applying an external electric field, it is possible to tune the Fermi energy level

[1], [2] (Fig. 1.4). Ideally, suspended graphene exhibits no doping, so the resistivity ( $\rho$ ) presents its maximum value at 0 gate voltage (" $V_g$ "). Depending on the applied positive or negative gate voltage, it is possible to tune the Fermi level to the conduction band or valence band, respectively. A positive gate voltage provokes a n-doping in the graphene and vice versa. Another aspect which pushes the research towards graphene technology is given by the results obtained in terms of carrier velocity with respect to the applied electric field

Fig. 1.5: Comparison of electron velocity versus electric field between graphene, CNT and conventional semiconductors. Source: adopted from [3].

(Fig. 1.5). In particular, higher values have been predicated and reached [20] showing a no drop compared to the III-V semiconductors [3] (Fig. 1.5). As a drawback due to the graphene zero bandgap and its semimetal behavior is its application for logic switching devices [21], even if several efforts have been devoted to open a gap and to overcome this issue [22]–[24].

### 1.3 Graphene optical properties

Thanks to graphene remarkable properties, it has been widely employed even for photodetection [25], [26]. Graphene "limit" due to its semimetal nature becomes a peculiar point, in the optoelectronics field, since it could potentially break the "long wavelength limit" of the convectional semiconductors which are transparent to the light with photon energy smaller than their bandgap. Its gapless nature in addition to its ultrafast carrier dynamics [26], [27], wavelength-independent absorption [26], [28], from the X-rays to the Terahertz frequencies [29], [30], with a flat optical absorption of 2.3% in the range from 300 to 2500 nm [6], [25], [31], tunable optical properties via electrostatic doping [26], [29], are the main characteristics which lead the success of such material in optoelectronics. As a drawback, pure graphene-based devices show poor photodetection performances, mainly due to both the small optical absorption [6] and the short charge recombination lifetime [7]. Photovoltaic, photo-thermoelectric, bolometric and photogating effects are the main mechanisms responsible of light detection in graphene-based devices [26], as it will be described in the following sections.

#### 3.1.1 Photodetection mechanisms

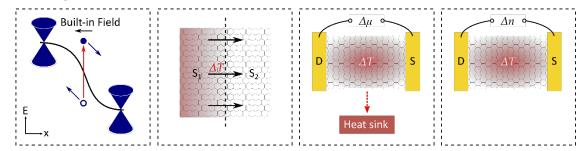

The above-mentioned photodetection mechanisms are shown in Fig. 1.6 and described in the following.

Fig. 1.6: From left to right: Photovoltaic effect, Photo-thermoelectric Effect, Bolometric Effect and photogating effect [26].

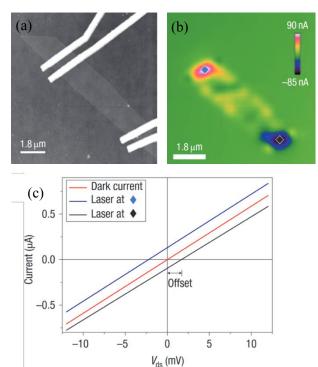

#### 1.3.1.1 Photovoltaic effect

Thanks to its 2D structure, graphene can be easily employed as photodetector, merely, by placing it longitudinally in between two contact electrodes (Source and Drain). By applying an incident light, electron-holes pairs photogenerated are separated by a built in electric field which occurs in between n-doped and p-doped graphene or between to different doped region [26], [32]. The involved built-in field could be induced exploiting the difference between graphene and contacting metal work function [33], or by a local chemical doping [34] or by using split gates [32]. The electric field could be also externally applied, but since the semimetal nature of

graphene, it is avoided, due to large dark current generation. Experimental results have been obtained on a device governed by this effect [35]. A picture of a scanning photocurrent measurement is shown in Fig. 1.7(b) where the device has been measured at zero source-drain and bias. As can be seen, the most part of photogenerated current occurs at the two metal contacts compared to the negligible current along the sheet where the small yellow dots are due to the presence of local built-in electric fields. The photogenerated current provokes a shift of  $I_d vs V_{ds}$  curve at the contacts when irradiated (Fig. 1.7(c)). Such a behavior reveals that metal electrodes play a fundamental role in the photoresponse in graphene-based devices [35].

Fig. 1.7: a) AFM micrograph of monolayer graphene flake connected by gold source-drain contacts, b) Scanning photocurrent measurements, c)  $I_d$  vs  $V_{ds}$  characteristics measured in dark condition with the laser beam located on the drain/source contacts. Source: adopted by [35].

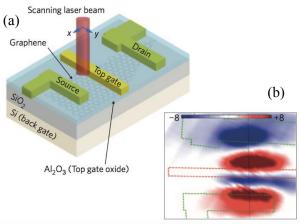

#### 1.3.1.2 Photo-thermoelectric effect

Photo-thermoelectric effect (PTE) is another mechanism which involves carrier generation in graphene. When graphene is exposed to an electromagnetic irradiation, the photogenerated electron-hole pairs provoke an ultrafast ( $\sim fs$ ) carriers heating (Hot carriers) [36]. The

photogenerated hot carriers remain at the same temperature thanks to graphene high phonon energy [37]. Such temperature, higher than the lattice, remains for picosecond, so the equilibrium is restored via scattering between acoustic phonons and charge carriers ( $\sim ns$ ) [38]. Such hot electrons produce a photovoltage which depends on the Seedback coefficients of the two graphene doped regions and on their temperature gradient ( $V_{PTE} = (S_1 - v_1)^{-1}$ ).

Fig. 1.8: a) Schematic of the device used to evaluate the PTE effect, b) Scanning photocurrent of the device. Source: adopted from [39].

$S_2 \Delta T_e$ ). PTE graphene detectors can achieve high bandwidths compared to PV detectors [26].

Graphene-based photodetectors based on such mechanism have been already exploited [39]. A schematic of the double gate used to evaluate the PTE effect and a scanning photocurrent are shown in Fig. 1.8(a). The photocurrent response has been measured by applying a laser beam with a wavelength  $\lambda = 600$  nm, without source-drain bias and zero back gate voltage applied. Both positive and negative photocurrents have been measured closer the drain contacts and at the edge of the top gate contact due to electron and hole photocurrent (see Fig. 1.8(b)). Due to the high temperature at the generated p-n junction thermoelectric current has been induced through the junction.

#### 1.3.1.3 Bolometric effect

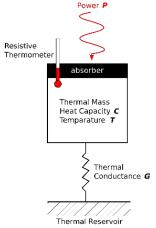

A bolometer consists in a device which measures the heating of a material having a temperaturedependent electrical resistance [40]. In particular, by applying an electromagnetic irradiation with

a specific incident power, an increment of the temperature can be converted by an absorption layer which converts the light into heat. The most important parameter associated to a bolometer is the thermal resistance  $R_h = \frac{dT}{dP}$ , where  $C_h$  is the specific heat of the bolometer and dP the absorbed power. Such parameters permit to calculate the response time  $\tau = R_h C_h$  [41]. Graphene is an appealing material if used as bolometer since presents low  $C_h$  thanks to the small volume for a given area and, in addition, the inefficiency of electron cooling by acoustic phonons, which means that  $R_h$  is high, thus the bolometric sensitivity results high

Fig. 1.9: Conceptual schematic of a bolometer.

as well [26]. Based on the change of the conductivity of the material due to the heat, an external bias is required and it does not need a p-n junction. This mechanism can be induced by a change

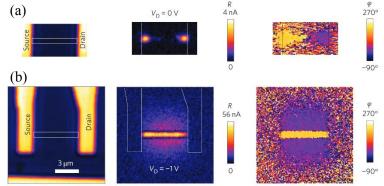

of the carrier mobility due to the heat or by the change of the number of carriers [26]. Experimental measurements on graphene-based photodetectors exploiting this mechanism are reported in the following[42] and shown in Fig. 1.10. On such experiments both bolometric

and shown in Fig. 1.10. On such experiments both bolometric both bolometric Fig. 1.10: a) Measured photocurrent (magnitude and phase) at  $V_D=0$  V drain bias and  $V_g=5V$  gate bias (n-type regime). (b) Photocurrent magnitude and phase at  $V_D=-1$  V drain bias and  $V_g=5V$  gate bias (n-type regime).

and photovoltaic effects are identified, but it has been demonstrated that the operating conditions are the cause of the photogeneration mechanism involved. Particularly, without applied bias, the

contribution of the photocurrent is due to the PV effect as can be seen from the vicinity of the photogenerated current with the metal contacts (Fig. 1.10(a)). Instead, by applying an external electric field, the photogeneration arise almost uniform in the whole graphene sheet (Fig. 1.10(b)).

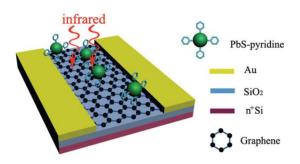

#### 1.3.1.4 Photogating effect

Photogating effect is a photogeneration mechanism based on the change of the material conductance as a consequence modification of the carrier density induced by the light [26]. In this mechanism, the electron-hole pair can be generated in graphene and then one carrier type can be trapped in charge traps, or photogenerated in charge traps or nanoparticles closer to the graphene sheet. For this photodetection mechanism a gain is provided which is dependent on the mobility

of the material: therefore, for this reason, graphene is an optimum candidate. As a drawback, high dark current values can be reached since an external electric field has to be applied. Hence, not very high responsivity values can be reached. To overtake this issue, regarding IR photodetection, graphene functionalization has been exploited, in particular by using quantum dots [43], which can absorb IR light more efficiently. In

Fig. 1.11: Schematic of the grpahene-based photodetector expliting the photogating effect. Source: adopted by [43]

particular, NIR photodetectors has been exploited by achieving  $10^7 A/W$  as photodetector responsivity [43].

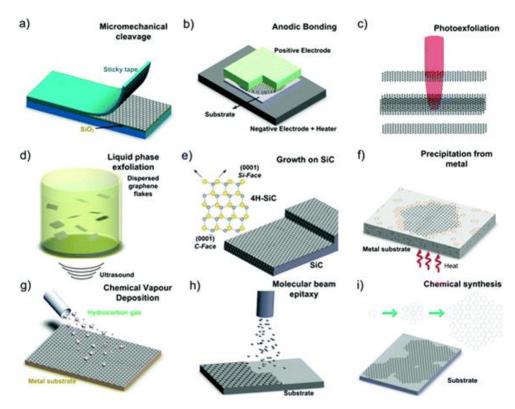

# 1.4 Graphene growth techniques

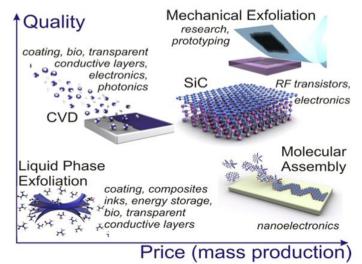

The production of graphene with specific properties for each application is the key issue for the diffusion of graphene-based devices. Different growth techniques have been developed since graphene discovery [4]. The common ones are depicted in Fig. 1.12 and the most used are subsequently described [44]–[46].

Fig. 1.12: Graphene growth techniques. Source: adopted by [46].

Micromechanical cleavage (MC), also known as micromechanical exfoliation, has been widely employed by crystal growers and crystallographers. Single Layer Graphene (SLG) can be achieved, thanks to MC procedures, by cleaving the graphene layers from the bulk graphite surface using an adhesive tape [1], [47]. Most of the prototypes are usually obtained using mechanical cleavage, since the quality of the obtained flakes is very high, in terms of mobility. As a drawback, such technique cannot be used for large scale applications. Nevertheless, MC remains ideal to investigate new physics and new device concepts.

Chemical Vapor Deposition (CVD), is nowadays a promising way to produce large scale polycrystalline graphene films on copper foil [48]. Due to the importance to the wafer scale integration [49], many efforts have been made to growth as much graphene with the compromise to obtain both high carrier mobility and uniformity of the film. A drawback of such technique is that a subsequent transfer of the graphene film from the copper foil to the achieved substrate is required [50]. Such post-treatment often affects the final quality of the graphene film [51] since it requires the use of PMMA mask, water intercalation methods, introduction of metallic impurities [52] and so on.

Synthesis on SiC. Graphitic layers can be grown on the silicon or carbon faces of a SiC wafer by sublimating Si atoms, obtaining a graphitized surface. The C-terminated face of SiC is used to

grow a stack of randomly oriented polycrystalline layers [53]. The graphene quality obtained employing this technique can be very high, but the drawbacks consist in the very high cost of the SiC wafer and the high temperature needed [44].

Liquid-phase exfoliation of graphite. Such a technique is based on the graphite exfoliation in a solvent by using ultrasounds to separate single and multilayer graphene. The solvents could be both aqueous [54] and non-aqueous [55]. A subsequent purification of the flakes is needed in order to separate the exfoliated to the un-exfoliated ones through centrifugation [45].

Laser ablation and photo-exfoliation is a technique which employs a laser pulse to ablate/exfoliate graphite flakes [45]. Such technique has been used for direct laser irradiation of graphene oxide (GO) obtaining promising results [56] for further improvements.

Depending on the fabrication methods, it is possible to obtain a compromise in terms of quality and costs as reported in Fig. 1.13 [44]. MC continues to be widely employed for the production of prototypes due to high quality graphene achieved, although the high cost prevents its use for mass production. CVD technique, instead, allows

Fig. 1.13: Map of graphene quality versus mass production. Source: adopted from [44]

large area monolayer graphene

growth. The "high-yield" and the relative cheapness of CVD graphene make this technique the primary candidate for large-scale electronics[49]. Graphene growth on SiC allows also high quality, large areas, films production. However, the high cost of the SiC wafers, the high temperatures (above 1000°C) used during the process and the incompatibility with silicon electronics technology make this technique not very feasible yet. In this work thesis, CVD monolayer polycrystalline graphene has been employed.

# 2. Graphene-based devices

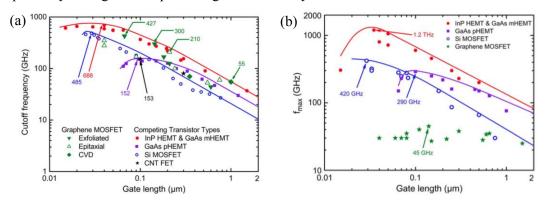

Thanks to its electrical and optical properties, already described in the previous chapter, graphene represents an ideal candidate not only to overcome actual well-established technologies but also, given its 2D nature, to be integrated within them. Since the large development of Silicon technology, its replacement by a novel material would not be a completely smart idea [3]. Therefore, many efforts have been made and to exploit novel technologies which could improve significantly the performances of existing technologies in electronics and optoelectronics fields. Unfortunately, the high cost, the low efficiency and, somehow, the low quality of graphene growth and patterning techniques are the limit of such material [45]. However, the excellent graphene properties inspired great interest to make use of such material on the realization of high frequency electronics and ultra-fast photodetectors. In this chapter, the adoption of graphene in such fields is reported. A short review on the-start-of art of graphene field effect transistors (GFETs) and graphene-based photodetectors will be presented in order to compare the obtained experimental results with the ones in the literature. Concerning high frequency application, before talking about novel transistor geometries it is fundamental to start with the introduction of the classical Metal-oxide-semiconductor field-effect transistors (MOSFETs) in order to let understand their limit and try to explain why the adoption of a novel material is needed. Its success is due to performance improvement thanks to the continuous scaling of its geometry [57]–[59]. MOSFET consists of a channel region connecting source and drain electrodes, and a barrier separating the gate from the channel [60]. The channel conductivity is controlled by a voltage applied between the gate and the source, i.e. V<sub>GS</sub>. To speed up the operation of such devices, a quick response to variations of V<sub>GS</sub> is needed, so the most important requirements are fast carriers in even shorter channel. The scaling down of the MOSFET geometry leads to the well-known "short-channel effects", i.e. threshold-voltage roll-off, drain-induced barrier lowering, and impaired drain-current saturation [61]-[63]. Nowadays, Si MOSFETs with 20-nm gates are already in mass production, but the further scaling and the simultaneous achievement of better device performance become more and more difficult. Nevertheless, different efforts have been made on the development of non-classical MOSFET architectures [59], [64] and meanwhile, this leads research to introduce devices based on a fundamentally different physics or on materials different than silicon. In this scenario, graphene obtained a great success, since its peculiar electrical properties [2], [3]. Graphene-based transistors can be employed in both digital and radiofrequency electronics. Due to the graphene nature and its zero band-gap, a low on-off ratio has been demonstrated in GFETs and this makes them unusable ("up to now") in the field of logic applications [3] even if recently, ON-OFF ratios around 100 and 2000 at room temperature and 20K have been obtained [24], revealing the great potential of bilayer graphene in digital electronics. Regarding radio-frequency (RF) electronics, materials with high carrier mobility are needed [3] even if their ON-OFF ratio is poor. Graphene properties make it the ideal candidate to improve ultrafast high-performance transistors. The most important figures of merit (FOM) describing the high-frequency performance of a FET are the transit frequency  $f_T$  and the maximum oscillation frequency  $f_{max}$ .  $f_T$  is the frequency where the circuit current gain  $|h_{21}|$  approximates unity,  $f_{max}$  instead is the frequency where the maximum oscillation power gain  $G_{MAX}$  is equal to 1 [65]. These FOM specify up to which frequencies the transistor offers current and power gain, respectively. In Fig. 2.1 the promising results already obtained are shown.

Fig. 2.1: Comparison of  $f_T(a)$  and  $f_{max}(b)$  of graphene MOSFETs versus gate length and  $f_T$  performance of CNT FET, InP HEMTs, GaAs mHEMTs, GaAs pHEMTs; and SiMOSFETs. Source: adapted from [3]

With regard to the optoelectronic field, instead, as reported in paragraph 3.1.1, different photoresponse mechanisms can be exploited to fabricate graphene-based photodetectors aimed to collect and convert photons to an electrical signal [26], [44], [66]. To evaluate the quality of photodetection, several FOM are commonly used, such as the external quantum efficiency (EQE), which is given by:

$$EQE = \frac{I_{ph}}{q\phi_{in}} \tag{2.1}$$

where  $I_{ph}$  is the measured photocurrent,  $\phi_{in}$  is the photon flux and q the electron charge. EQE represents the quantity of e-h pairs detected per incident photon [67]. To evaluate the photodetection efficiency the internal quantum efficiency (IQE) is used:

$$IQE = \frac{I_{ph}}{q\phi_{abs}} = \frac{EQE}{A_{abs}}$$

(2.2)

where  $\phi_{abs} = A_{abs}\phi_{in}$  is the absorbed photon flux and  $A_{abs}$  is the absorbed fraction. This FOM gives the photodetector ability to transduce the absorbed photons to an electrical signal. The sensitivity, instead, is described by its responsivity R which is given by the ratio of the photocurrent to the incident power:

$$R = \frac{I_{ph}}{P} = EQE \frac{q}{hv} \tag{2.3}$$

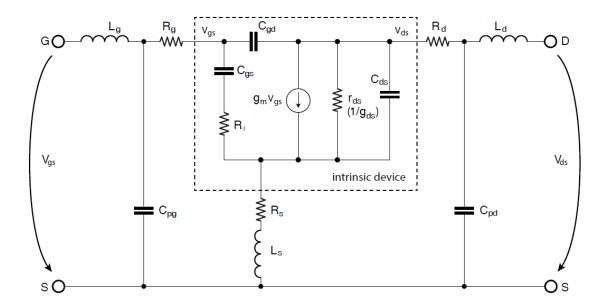

## 2.1 Graphene field effect transistors (GFETs)

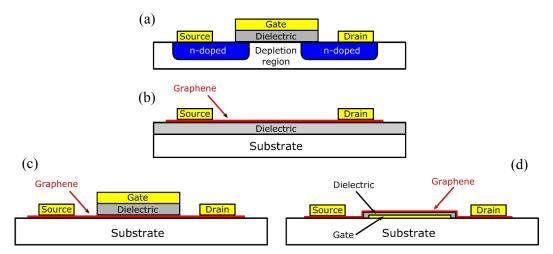

Graphene field effect transistors (GFETs) is the name given to the novel devices exploiting graphene as channel layer. Several GFET layouts have been designed, fabricated and characterized in order to reach better performances compared to well-known ones, exploiting graphene properties [3], [68]–[70]. Herein, a comparison of standard Si-MOSFETs and different GFETs geometries is reported. In Fig. 2.2 cross sections of a standard Si-MOSFET and three different types of GFETs are shown. A distinction between GFETs with local and non-local gate structure is also reported. Fig. 2.2(b) refers to a non-local gate structure, also called back gate GFET while (c) and (d) refer to a local, top and bottom gate, respectively.

Fig. 2.2: a) Schematic of a n-type semiconductor-based FET. (b) GFET with back gate structure, (c)GFET with local top gate and (d) local bottom gate.

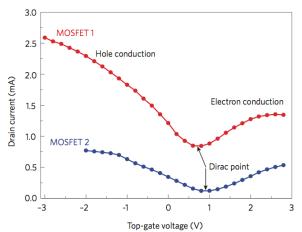

Back-gate devices have been very useful for research purposes, but since the presence of 300nm silicon oxide layer and doped silicon as back gate, large parasitic capacitances are reached [1]. Additionally, poor gate efficiency and the impossibility of integration makes this configuration vain for further performance improvements [3]. GFETs with local top gate structure, instead, can exploit the flatness of the deposited graphene sheet but the subsequent oxide layer deposition usual degrades graphene mobility [71]. Local bottom gate structures, instead, could exploit higher values of graphene mobility, even if large flat areas are more difficult to obtain. In order to characterize such devices, since graphene-based transistors are affected by hysteretic behavior simultaneous DC and RF characterizations have to be performed. By starting from the typical

transfer characteristics obtained in [72], [73], as it can be seen in Fig. 2.3, by applying an external

bias i.e. drain-source voltage " $V_{DS}$ " and by sweeping the gate-source voltage " $V_{GS}$ ", it is possible to tune the graphene Fermi level, and thus to dope the channel depending on the applied  $V_{GS}$ . Large positive gate voltage causes channel electron accumulation (n-doping) and vice versa. In particular, it has to be noticed that, after graphene transfer process on the desired substrate to fabricate transistors, it usually reaches an intrinsic doping [34], [74]. As can be seen in Fig. 2.3, the two

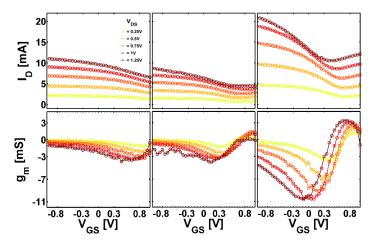

Fig. 2.3: transfer characteristic for two characterized GFETs. Source: adopted by [3]

estimated Dirac points are not located at  $V_{GS}=0$ , but they are slightly shifted in one direction (p-doping in this case). As a consequence of the increment of  $V_{DS}$  values, the Dirac point continues to shift as it can be seen in the following chapter based on the experimental work. The transcharacteristic curves are also fundamental for the further RF measurements, since their slope determinates an important FOM for RF characterization, which is named transconductance  $(g_m)$ . Such a value describes how effective the gate voltage modulates the drain current. It is defined as the partial derivative of  $I_{ds}$  with respect to  $V_{GS}$  at given operating point  $V_{DS}$ :

$$g_m = \frac{\partial I_{ds}}{\partial V_{GS}}\Big|_{V_{DS=const}}$$

(2.4)

By looking at the transcharacteristic curves, their highest slope determinates the highest transconductance values, so further RF characterization based on the S-parameters measurements

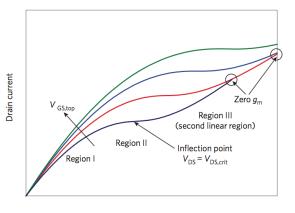

has to be carried out in the particular range of  $V_{GS}$  and  $V_{DS}$  around this value in order to reach the best device performances in terms of gain,  $f_T$  and  $f_{MAX}$ . The same behavior, of course, occurs by looking the I-V device curves (output characteristics) (see Fig. 2.4). No saturation [75] or only weak saturation [69], [76] can be seen. Three different region can be considered, the first where the curves have a linear shape, for small values of  $V_{DS}$  and the channel is n-type (region I). By increasing the

Drain-source voltage

Fig. 2.4: qualitative shape of the GFETs output characteristics. Source: adopted by [3]

$V_{DS}$  values, a principle of saturation can be seen (Dirac point) until the inflection point at  $V_{DS}$  =

V<sub>DS,crit</sub> is reached (region II). By further increasing the V<sub>DS</sub> value over the V<sub>DS,crit</sub>, the channel switches from n-type to p-type [77], [78] and the curves show again a linear behavior (region III). All the DC curves shown have been reached without emphasizing a well-known problem of the hysteresis in graphene-based devices[79]. Another very important drawback which crucially affects graphene-based devices performances is the contact resistance between graphene and the metal electrodes. In the following paragraphs both issues will be shortly explained, in order to understand the limitation induced on such devices and the methods used to overtake them.

## 2.2 Hysteresis in graphene-based devices

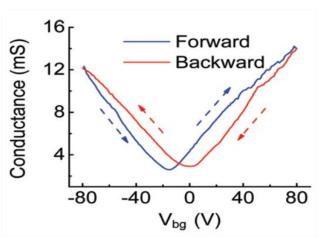

As preliminary discussed, hysteresis represents an important issue in graphene-based devices, since it leads to an instability of the operating point and thus in their practical usage [79]. Both the transfer characteristics and the drain conductance, being related, exhibit shifts depending on the gate/drain sweep measurement procedure leading to a not univocal operating point of the device under study. A typical hysteretic behavior in graphene-based devices is shown in

Fig. 2.6: Conductance vs gate voltage curves measured in ambient condition. A hysteresis behavior is observed when backward V<sub>GS</sub> sweep is performed. Source: adopted by [79].

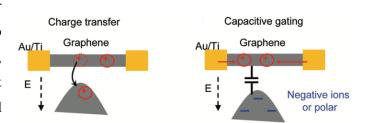

Fig. 2.6. As reported in [79], there are two main mechanisms involved in the phenomena (see Fig.

2.5). First, the charge transfer (holes/electrons) from graphene to charge traps in the oxide and second, the capacitive gating. In the first mechanism, by looking the forward sweep, due to the initial graphene p-doping, holes transfer from graphene

Fig. 2.5: Schematic of the two mechanisms involved in the hysteretic behavior of graphene-based devices

to the charge traps in the oxide. This increases the gate effective potential if compared with the applied external voltage, and thus, the Dirac point is reached by applying a lower  $V_{GS}$  value, vice versa for n-doping. Instead, capacitive gating occurs when the charged ions alter the local electrostatic potential around the graphene, which pulls more opposite charges onto graphene from the contacts.

#### 2.3 Contact resistance

Graphene/metal connections are necessary and at the same time fundamental for the fabrication of performing devices. In particular, not only choice of the right metal [80], but even the way to connect it to graphene [81], [82] significantly influence device contact resistance "R<sub>c</sub>"[83] which is a performance killer for the high performance graphene-based transistors [84]–[86]. The use of metal contacts leads to an induced graphene doping [87] depending on the difference between work function between metal and graphene [80]. It has been studied that the adoption of copper, nickel and palladium alter by chemisorption graphene electronic transport, while aluminum, silver and gold only cause small alterations in the band structure due to the weak bonding [80]. Moreover, high work function difference has effect on the contact resistance reduction [23], [83], [84], [88], [89]. As a drawback, it leads to formation of a p-n junction in the channel region [84]. Different efforts have been made to reduce contact resistance values, such as post annealing procedures or contacting graphene from both sides [90] by using Ti/Pd contacts. "End-contacting" graphene at the edges has been demonstrated as a promising exploit in order to reduce graphene contact resistances [81], [91].

#### 2.4 State of art of GFETs

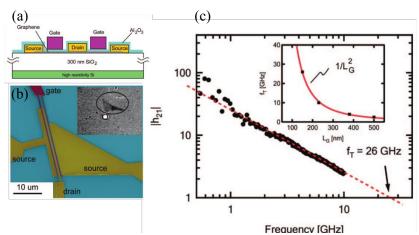

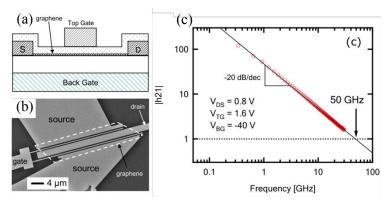

Several works have been published concerning the evolution of GFET device performance and they are summarized in the following. In 2009, IBM published the first work on GFET representing a significant step toward the realization of graphene-based electronics for high-frequency applications [75]. Top-gated graphene transistors have been fabricated and their

characteristics analyzed at microwave frequencies. This work highlights that measured intrinsic GFET current gain shows an ideal 1/f frequency dependence, indicating a FET-like behavior for graphene transistors. They claimed that  $f_T$  increases reducing the gate length, and a

Fig. 2.7: (a) Schematic cross section of the graphene transistor (b) scanning electron microscopy image of the graphene channel and contacts. (c) Measured current gain  $h_{21}$  as a function of frequency of a GFET with  $L_G = 150$  nm, showing a cut-off frequency at 26 GHz. [75].

value of 26 GHz has been measured for a graphene transistor with a gate length of 150 nm and

carrier mobility of 2000  $cm^2/Vs$ . Due to the chemically inert behavior of graphene surfaces to atomic layer deposition precursors, NO<sub>2</sub> functionalization has been employed for the subsequent Al<sub>2</sub>O<sub>3</sub> deposition. The limitation in the frequency response of the fabricated devices has been attributed to charged impurity scattering associated with the functionalization layer and interface phonon scattering in the oxide which leads to current and mobility degradation.

In 2010, a dual-gate graphene field-effect transistor with higher mobility values (2700  $cm^2/Vs$ )

has been obtained [92]. A cut-off frequency of 50 GHz has been demonstrated in a 350-nm-gate-length device by reducing the access resistance using electrostatic doping and 2-nm of Al (first deposited and then oxidized) to serve as nucleation layer for the subsequent ALD-deposited film. The poor high

Fig. 2.8: (a) Device schematic of the dual-gate graphene transistor. (b) SEM image of a dual-channel graphene transistor. (c) RF performance shows a current gain at -20dB/dec and a cut-off frequency  $f_T$  of 50GHz [92].

frequency performances are essentially due to the high capacitance induced by the conductive substrate used.

Both the above-mentioned examples refer to GFET employing exfoliated monolayer graphene.

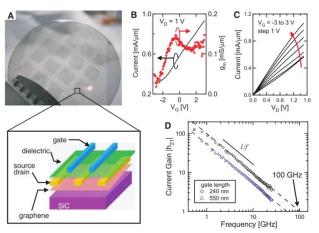

As reported before, large scale devices are not feasible employing this technique. In 2010 IBM group reported the performances of a matrix of GFETs on SiC wafer exhibiting 100GHz cut-off frequency [93]. Epitaxial graphene growth on SiC with thermal annealing at  $1450^{\circ}$ C has been used. The reported estimated mobility was in the range  $1000 \div 1500 \ cm^2/Vs$ . Arrays of top-gated FETs were fabricated with various gate lengths (L<sub>G</sub>), with the shortest being 240 nm. In order to form the top gate stack, an interfacial polymer layer made of a derivative of poly-hydroxystyrene was

Fig. 2.9: (a) Image of devices fabricated on a 2-inch graphene wafer and schematic cross-sectional view of a top-gated graphene FET. (B) Drain current versus gate voltage at drain bias of 1 V and (C) Drain current as a function of V<sub>D</sub> for various gate voltages of a GFET with L<sub>G</sub> = 240 nm. (D) Measured small-signal current gain |h<sub>2</sub>| versus frequency for a 240-nm-gate and a 550-nm-gate GFET at V<sub>D</sub> = 2.5 V showing 100 and 53 GHz, respectively. Source: adopted by [93].

spin-coated on the graphene before the atomic layer deposition of a 10-nm-thick HfO<sub>2</sub> insulating layer [94].

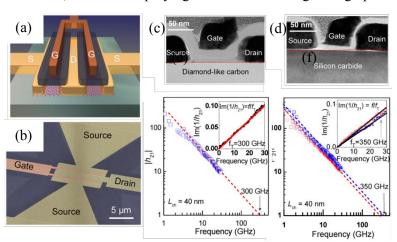

Finally, in 2012 Wu et al. [70] focused their work on an optimized GFET architecture with an intrinsic cut-off frequency of 300 GHz, obtained employing wafer-scale CVD grown graphene

on diamond-like carbon (DLC), and of 350 GHz for epitaxial graphene on SiC. For CVD graphene on DLC, the top-gate dielectric stack includes an electron-beam evaporated and oxidized Al layer followed by an atomic layer deposited (ALD) film of Al<sub>2</sub>O<sub>3</sub> [95]. For epitaxial graphene, 15 nm silicon nitride was grown by plasma-enhanced **CVD** (PECVD) at 400 °C [96].

Fig. 2.10: (a) Schematic view of a top-gated graphene RF transistor on a DLC substrate. (b) SEM image of top-gated dual-channel RF device. Cross-section TEM images of a transistor based on CVD graphene on DLC(c) and on epitaxial graphene on SiC (d); |h21| versus frequency for the 40 nm device with  $f_T = 300$  GHz for GFET on DLC (e). (f) and for two 40 nm GFETs on SiC with  $f_T = 300$  and 350 GHz [70].

### 2.5 State of art graphene-based photodetectors

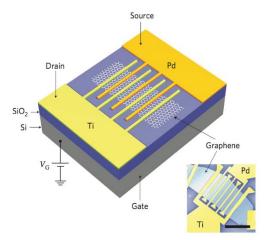

As preliminary discussed in par. 1.3, by exploiting both graphene ultra-high carrier mobility and

short carrier lifetime, a metal-graphene-metal photodetector has been fabricated and characterized [7]. Since the built-in electric fields take place in a small region close to metal/graphene interfaces [97], interdigitated metal finger has been designed above the graphene sheet to enhance the PV effect by increasing the detection area (see Fig. 2.11). Such device has been employed in a  $10~Gbit~s^{-1}$  optical datalink, reaching a maximum external responsivity of R = 6.1~mA/W at  $1.55~\mu m$ . In order to enhance the PV effect, the difference

Fig. 2.11: Schematic of the interdigitated metal-graphene-metal photodetector. Source: adopted by [7].

between graphene and metal source work function has been chosen higher than graphene and metal drain work function. 16 GHz as 3-dB bandwidth has been evaluated limited by the RC

constant of the device. Such experiment led graphene photodetector to be a promise candidate for

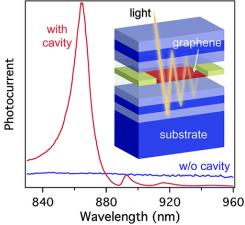

telecommunication application. As preliminary discussed, graphene absorbs 2% of incident light [6] which is a large value if compared to its atomically thickness but still not enough to reach high photoresponse values. Different configurations have been proposed in order to enhance the detection capability of such devices. Exploiting graphene-light interaction length, it has been integrated in an optical microcavity [98]. In Fig. 2.12 both the schematic of the fabricated device and the photoresponse achieved by using a bilayer device are shown. As it is possible

Fig. 2.12: Schematic of the graphene microcavity photodetector. Photocurrent results for bilayer graphene. Source: adopted by [98].

to notice, when exploiting multiple light absorption in graphene by using the microcavity, an enhancement of the photocurrent is reached if compared to the detector without cavity. A maximum external responsivity of 21mA/W has been achieved [98]. The limit due to integration

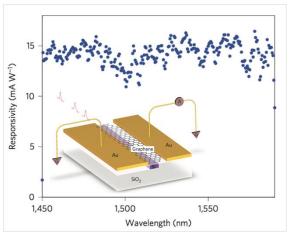

in such cavity is to restrict photodetection to narrow bandwidth. In order to overcome this issue, a proposed way to enhance graphene-based photodetector response has been to integrate graphene on a photonics waveguide [99], [100]. In particular, by coupling the evanescent field out of the waveguide in the graphene, a photoresponsivity of 0.1 A/W has been reached in a broad spectral bandwidth [99] as shown in Fig. 2.13. It has been demonstrated that another way to enhance graphene-based

Fig. 2.13: Responsivity of graphene integrated on photonics waveguide as photodetector. Source: adopted from [99]

photodetectors sensitivity is to exploit the excitation of surface plasmon by placing the plasmonic nanostructures close to the contacts [101]. When low intensity has to be detected, hybrid phototransistors can be employed which exploit the PV effect in efficient absorbing synthetized centers with the subsequent charge transfer in a conductor [26], [102].

# 3. Experimental activities

In this chapter, GFETs fabrication steps and the results of electrical (RF/Microwave) and optical characterization are reported. Starting from the choice of the most suitable substrate, first a statistical study on the layout influence on microwave performance has been made. Then, taking into account the role of the gate dielectric, a comparison of different thin oxide layers has also been performed. Finally, an optical characterization has been carried out aimed at exploiting GFETs use as visible and infrared photodetectors, with a wideband intrinsic gain capability.

#### 3.1 Substrate

The choice of the substrate plays a key role to enhance graphene-based devices performance, since graphene charge mobility is strictly connected to the scattering induced by the substrate [103]. High mobility values are needed in order to improve GFETs gains and cut-off frequency values in the MW regime and fast modulation in the photonics field. The first graphene devices have been fabricated on Si/SiO<sub>2</sub> substrates [1], [104], [105], exploiting the possibility to tune graphene Fermi level by using the highly doped Si as back gate and to use the stack (300nm of SiO<sub>2</sub> on the p-doped Si) to enhance the optical contrast under microscope view. However, it has been demonstrated that its use limits the graphene potential due to several issues, such as flatness, charge traps in SiO<sub>2</sub> forming "charge puddles" [106], which lead scattering, a low dielectric constant  $(\varepsilon_r \sim 4)$ , even though it offers high break-down voltage. Additionally, the low energy SiO<sub>2</sub> phonons enhance scattering phenomena [107]. Such substrate is also not suitable for high frequency electronics, as confirmed also by experiments/simulations already done. In fact, its physical properties imply high values of parasitic capacitances and losses. For this kind of applications, the optimal substrate should be flat, insulating, and free of charge traps. As reported in 2.4, GFETs showing the best performance have been fabricated on insulating or semiinsulating substrates [108]. In this framework, sapphire can be considered a good candidate [109], [110]. It exhibits low dielectric losses and good heat conduction in addition to high dielectric constants ( $\varepsilon_r = 9.39$  (E perpendicular to the C-axis) and  $\varepsilon_r = 11.58$  (E parallel to the Caxis)[111]). Sapphire resistivity is orders of magnitude larger than the one of high resistive Si [111], which leads to a reduction of the parasitic capacitances between the pads and the device launchers. Also, its high thermal conductivity [111] enables fast cooling and thus high current densities. In the optoelectronics field and, particularly, for telecom applications, sapphire does not represent a good substrate candidate due to its high band gap (it cannot provide carriers). Nevertheless, its use can help keeping graphene flatness after the transfer procedures. Due to the above-mentioned characteristics and for continuity with the experimental activity performed by

Dr. C. Benz, a former PhD student at KIT [112], in this work sapphire has been chosen as the substrate for graphene-based devices fabrication.

#### 3.2 Gate dielectric

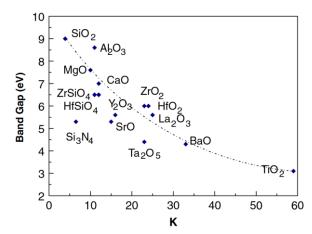

Once the substrate has been chosen, a good gate dielectric needs to be found to allow the development of competitive ultrafast transistors. Graphene surface is chemically inert to atomic layer deposition (ALD) precursors making the integration of high-dielectric constant materials a tricky process [71]. Fig. 3.1 shows the band gap versus the dielectric constant of some materials

commonly used as gate dielectric [113]. As well known, in MOSFET technology, a thinner oxide - i.e., a higher oxide capacitance (Cox) - is desired to maximize the device RF-performances since it leads to a higher value of the transconductance and, consequently, of the cut-off frequency. Unfortunately, a thin gate oxide causes two main drawbacks: high leakage current due to tunneling phenomena and poor long-time reliability [114]. As a possible solution, high

Fig. 3.1: Bandgap vs. dielectric constant of some common gate dielectrics. Source: adapted from [114]

$\kappa$ -oxide materials have been widely employed [115], [116]. Additionally, leakage current significantly depends on the conduction bands offset between the oxide and the semiconductor employed [114]. For these reasons, a trade-off should be found between oxide thickness and band offset. Traditionally, hafnium has been the most exploited oxide thanks to its high  $\kappa$  factor ( $\kappa \approx 25$ ). Titanium oxide exhibits a higher  $\kappa$ -value ( $\kappa \approx 80$ ), but it is thermally unstable when deposited over silicon. Aluminum oxide exhibits a too low  $\kappa$  value ( $\kappa \approx 9$ ), but shows a very high breakdown voltage [19]. In graphene, all the above mentioned oxides can potentially be used as gate oxide layers for field effect transistors fabrication. Atomic Layer Deposition (ALD) is a common way to grow dielectrics with an exact control on the thickness. Nevertheless, it cannot be used directly on graphene due to its inertness. However, by exploiting graphene small imperfections as nucleation centers, the growth could be possible [117]. In this work, for the fabrication of top gate devices, air oxidation of a thin layer of aluminum [95] deposited by Molecular beam epitaxy (MBE) has been exploited, which acts as seed layer for the further nucleation of the oxide film.

### 3.3 Fabrication techniques

In the following, the techniques used for fabrication steps of the samples are reported.

**Substrate cutting and cleaning**: 2 inches sapphire has been provided by Roditi [111]. Before starting the fabrication process, it has been cut into small pieces by a diamond pen. Then, the substrate has been soaked in acetone and put in the sonication for 20s. Afterwards, it has been cleaned again with acetone and isopropanol and placed in reactive ion etching (RIE) with oxygen plasma for 2 min in 0.2 mbar conditions. Subsequently, it has been backed in the hot plate at 200°C for 15 min.

Fig. 3.2: Substrate cutting and cleaning by using RIE

*Spin-coating of PMMA resist:* Poly (methyl methacrylate) (PMMA 4.5wt%) masks have been used for all the technological steps. PMMA has been spin-coated at 6000 rpm for 90s, resulting in an average thickness of 200nm. A subsequent backing on hot plate at 180°C for 1min has been made.

Fig. 3.3: Spin-coating of the PMMA as mask for all the technological steps

*Spin-coating of E-spacer:* Since sapphire is insulator, beam deflections occurs on the surface when PMMA masks are exposed by electron beam lithography. For this reason, E-spacer 300Z,

a conductive polymer from Showa Denko K.K., has been used as charge dissipation layer. In order to reach a good thickness homogeneity, it has been spin-coated at a speed of 3000 rpm for 60s with subsequent baking at 100°C for 45 s on the hot plate.

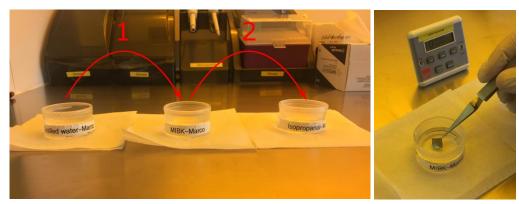

**Development of PMMA resist:** In order to develop the exposed PMMA masks, the E-spacer has to be removed by soaking the sample in distilled water. Subsequently, the resist has been developed in 1:3 MIBK:IPA for 15 s, soaked in isopropanol and then let it dry using a nitrogen gun.

Fig. 3.4: PMMA development procedure

Electron beam lithography (EBL): During sample fabrication, several consecutive steps of EBL have been performed in order to expose the PMMA masks for subsequent metal/oxide deposition or for graphene etching. Raith eLine EBL system has been used to write the patterns into the PMMA (Fig. 3.5). It operates at a maximum acceleration voltage of 30 keV with a gun pressure of  $6\times10^{-10}$  mbar and a chamber pressure  $<2\cdot10^{-6}$ mbar. High accuracy in the xy-movement (~2nm) is reached thanks to the interferometric stage. Depending on the aimed resolution, due the pattern dimensions, two different beam apertures have been used. The first consists of 20 μm aperture and a step size of 8nm used for the exposition of the inner part of drain, source, gate electrodes and graphene mask. The second, instead, consists of 120 μm aperture and a step size of 69nm for the exposition of the source, drain and gates coplanar waveguides and for the contacting pads.

Fig. 3.5: Raith "eLine" electron beam lithography system

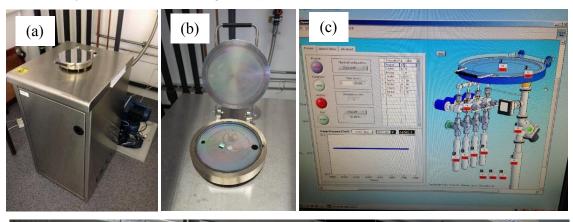

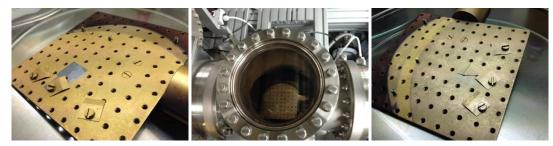

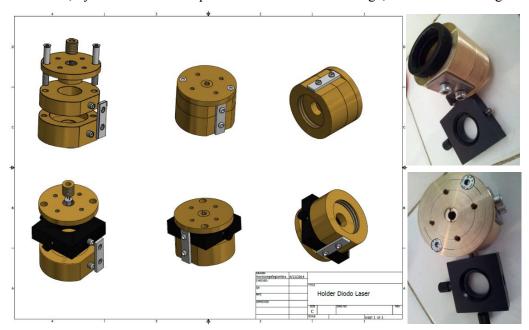

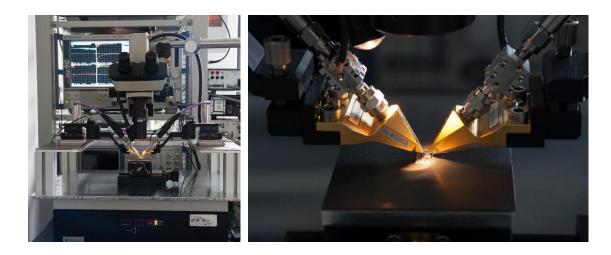

Atomic layer deposition (ALD): Atomic layer deposition has been used for the gate oxide deposition. This is a critical step, since the thickness, the uniformity and the quality of the deposited oxide have effect on the device performances, in terms of graphene mobility and gate capacitance. For my purpose, Cambridge Nanotech Savannah ALD (Fig. 3.6(a-c)) and R-200 Advanced system from Picosun (Fig. 3.6(d)) have been used.

Fig. 3.6: a-c) Cambridge Nanotech Savannah ALD, d) R-200 Advanced system from Picosun

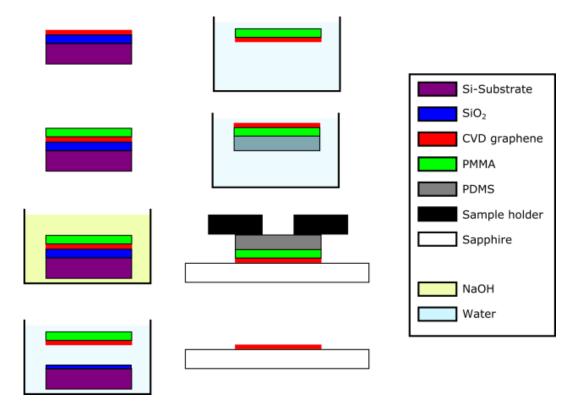

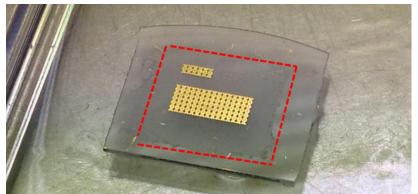

CVD Graphene transfer: Monolayer CVD graphene used in my work has been provided by Prof. M.H. Jang and Prof. J.-H. Ahn from the School of Electrical and Electronic Engineering, Yonsei University, Seoul, South Korea. It has been initially grown on copper foil and then transferred onto a SiO<sub>2</sub>/Si substrate using standard methods [118]. Since graphene has to be transferred again from such support to the aimed substrate (sapphire), all the steps used are illustrated in the Fig. 3.7

Fig. 3.7: Graphene transfer process sketch

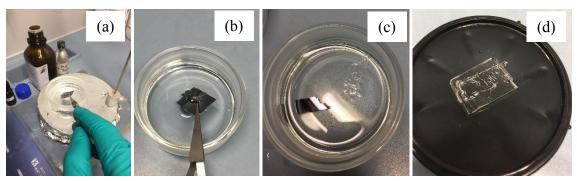

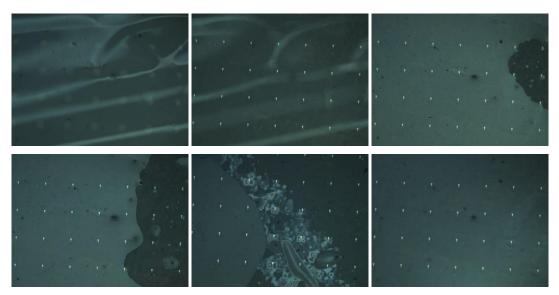

Around 800 nm of PMMA, (8wt%) has been spin coated onto the graphene layer. Such PMMA thickness guarantees at the same time a good elasticity and mechanical resistance. A PDMS adhesion layer has been used as a mechanical support to help the imprinting of the PMMA-graphene sheet (i.e. the assembly) on the target substrate. In order to help the detachment of the assembly from the substrate, the edges have been scratched and then the stack has been soaked first in a 1 mol NaOH solution to dissolve the thin SiO<sub>2</sub> layer (Fig. 3.8(a-b)) and then cleaned by soaking it in pure distilled water (Fig. 3.8(c)).

Fig. 3.8: Detaching of the assembly from the silicon substrate

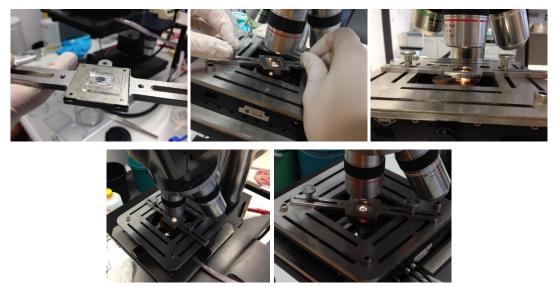

Afterwards, the assembly has been placed on a microscope glass to let it dry and then mounted on ad-hoc sample holder with a hole in the metal made to watch through and help for the further

alignment in the microscope (Fig. 3.9). Below the sample holder, the sample is placed on a hot plate at 60°C.

Fig. 3.9: Assembly placed on the ad-hoc sample holder for the transfer process on the arbitrary substrate

When the assembly touches the substrate, the temperature has been increased up to 120°C and it starts to adhere as shown in Fig. 3.10. The alignment has been controlled through the sample holder mounted on the optical microscope. Finally, after waiting for 5 min, the sample holder has been lifted up and both the PMMA and the graphene remains. A subsequent soaking in acetone and isopropanol has been performed to remove the PMMA residue.

Fig. 3.10: Graphene-PMMA-PDMS adhesion on the sample

Fig. 3.11: PMMA-graphene transferred on the sample

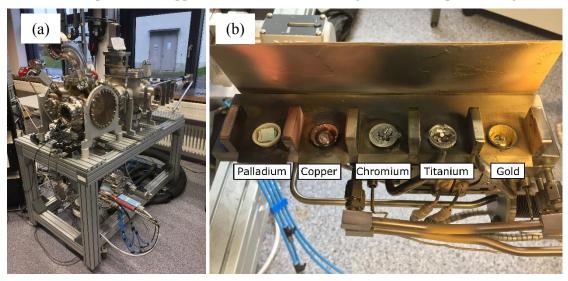

*HV metal evaporation*: For metal evaporation the system in Fig. 3.12a has been used. Different metals such as palladium, copper, chromium, titanium and gold can be evaporated (Fig. 3.12b).

Fig. 3.12: (a) HV metal evaporator (Schimmel group), (b) crucibles.

A high voltage (3 kV) electron beam is used to melt the targets, deflected by magnetic fields (xy-deflection). The system is equipped by a load-lock chamber in order to keep the very low pressure of the main chamber. Both the main and the pre-chamber, when both evacuated by turbomolecular pumps, reach a pressure of around  $10^{-7}$ mbar.

Fig. 3.13: HV Metal evaporation

*UHV metal evaporation:* Due to graphene inertness to atomic layer deposition precursors, a deposition of ~3nm of aluminum by the molecular beam epitaxy (Fig. 3.14) has been made in order to let it naturally oxides. This process has been necessary for the subsequent ALD oxide deposition.

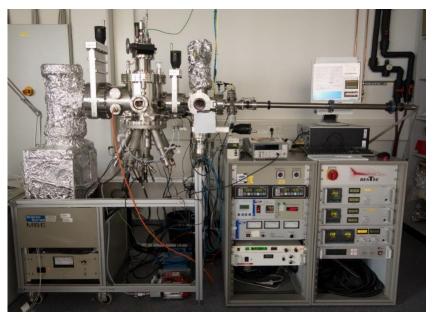

Fig. 3.14: UHV metal evaporator (Beckmann group)

*Lift-off*: In order to remove the PMMA mask after the metal/dielectric deposition a lift-off procedure has been performed. Both acetone and dimethyl sulfoxide (DMSO) have been used. In particular, after ALD deposition, since the material is deposited isotropically, even at the edge of the structure, soaking the sample in acetone is inefficient. Therefore, the sample, after applying scratches far away from the structures (in order to let the solvent, go through), has been soaked in DMSO at 70°C. For metal lift-off, instead acetone has been used. If graphene has not been transferred on the surface, sonication could help the lift-off but it is avoided after its transfer.

Fig. 3.15: lift off procedure

### 3.4 M4 Device

### 3.1.2 Design

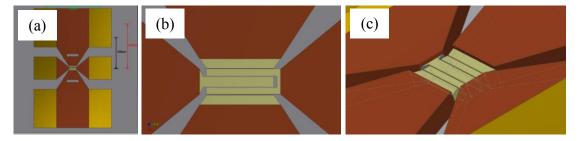

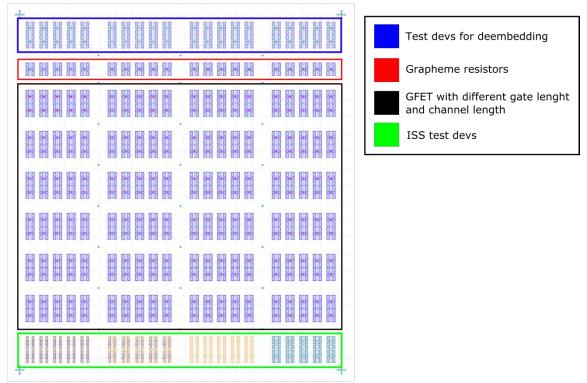

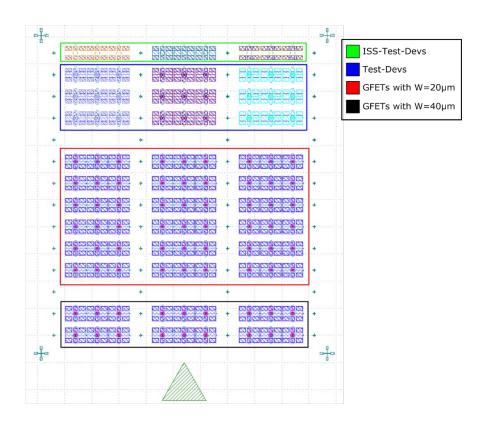

After choosing Sapphire as a good and promising substrate for graphene high-frequency electronics, a design of GFETs has been made selecting, at first, aluminum oxide for the gate dielectric. A top dual gate structure with coplanar waveguide has been used. The new design is composed of the extrinsic part (see orange in Fig. 3.16) and the intrinsic part (see yellow in Fig. 3.16). Thanks to this configuration, the extrinsic part (drain/gate tapered CPW launchers) remains the same for all the devices, including test-devices for the de-embedding procedure (A.4). Additionally, the vertical spacing between the input/output contact pads (Fig. 3.16(a)) has been chosen equal to that of the Impedance Standard Substrates (ISS) of the on-wafer calibration Kit (A.2.3). This aspect allows the design to keep always the same coupling capacitance.

Fig. 3.16: Sketch of the design of device M4

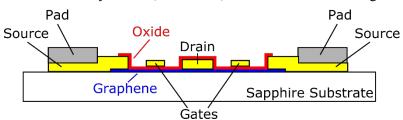

The cross section of this family devices, called M4, is shown in the following sketch, Fig. 3.17:

Fig. 3.17: Cross section of M4 family devices

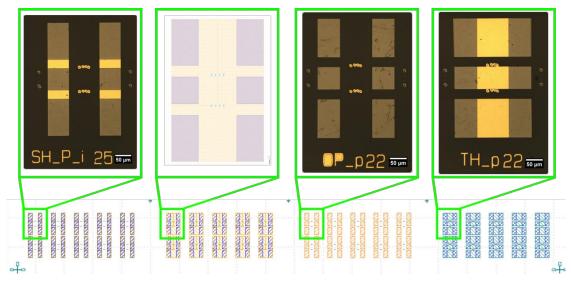

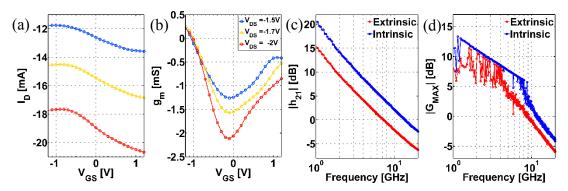

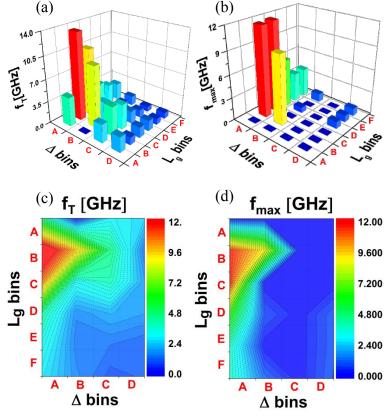

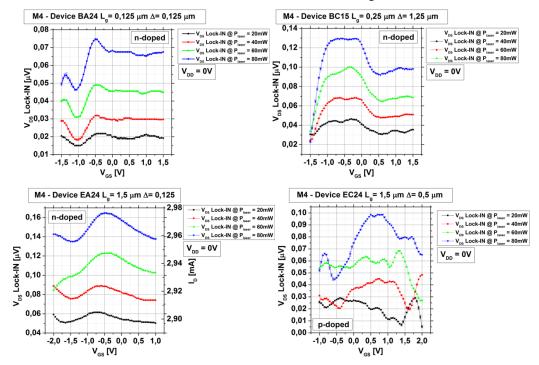

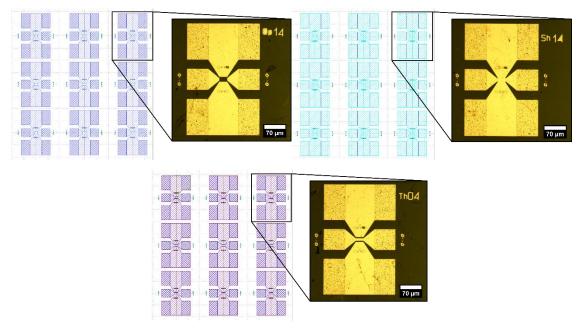

### 3.1.3 Layout influence on GFETs microwave performances

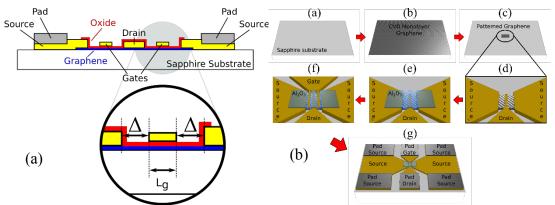

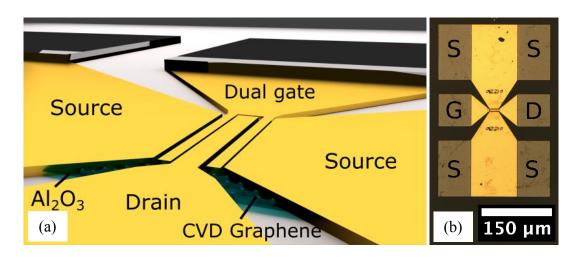

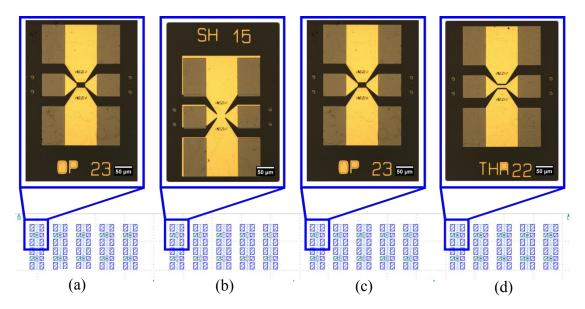

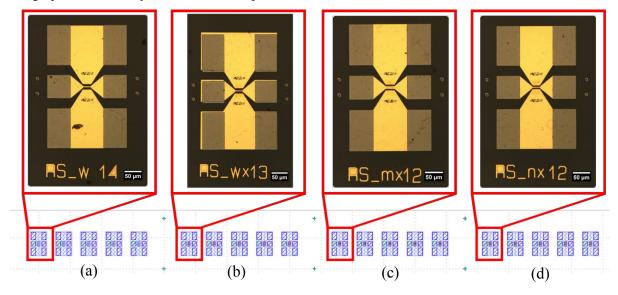

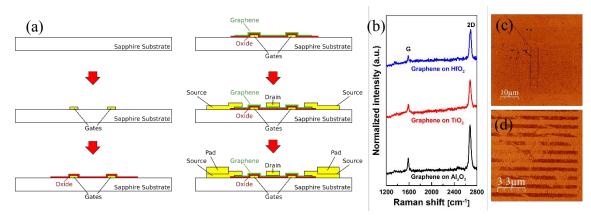

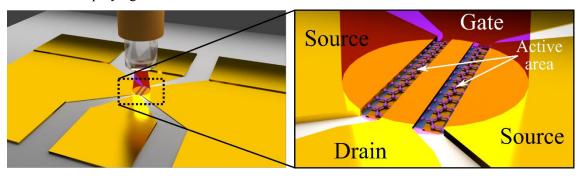

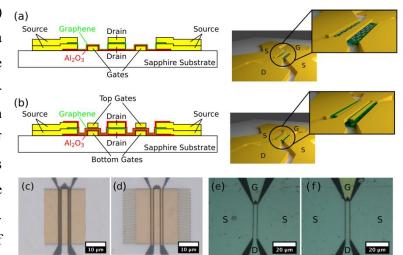

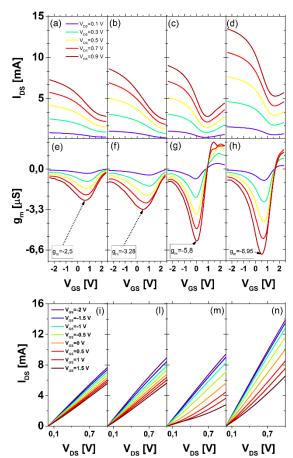

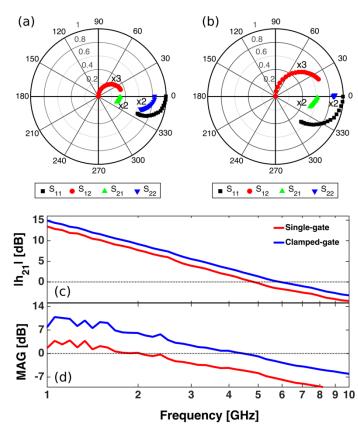

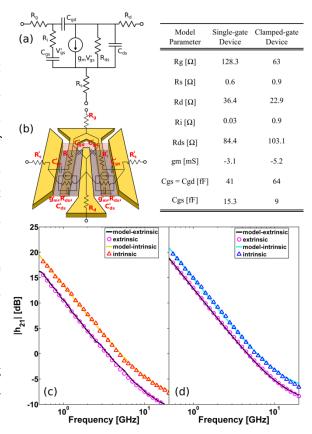

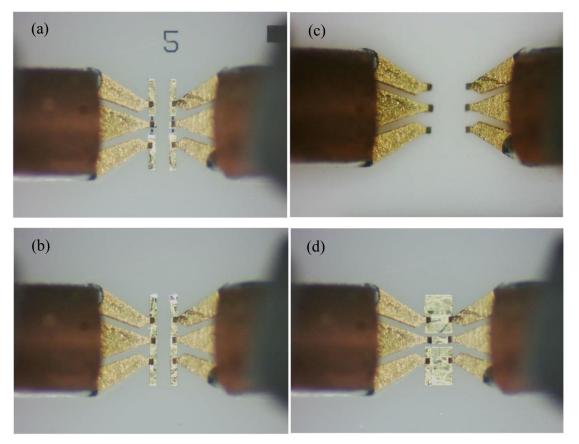

A statistical and parametrical investigation aimed at experimentally evaluating the microwave parameters dependence on GFETs dimensions has been made. In detail, the analysis has been carried out on samples with different geometries (i.e., varying both the gate-drain/source distance and the gate length) to study the layout influence on the device performances. The cross section of the devices is depicted in Fig. 3.18(a)

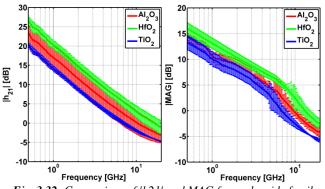

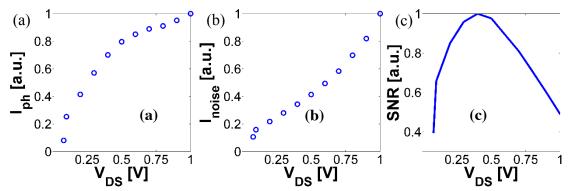

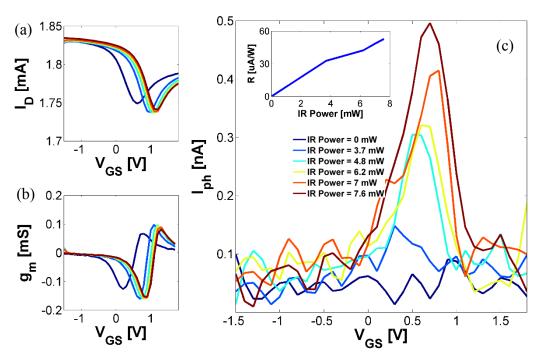

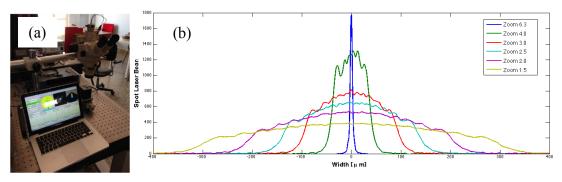

Fig. 3.18: a) Cross-section diagram of the GFET, b) Sketch of the fabrication process of GFETs