# UNIVERSITÀ DEGLI STUDI DI PALERMO

Department of engineering

Ph.D. in Electronic and Telecommunication Engineering

# Design, Implementation and Experimental Evaluation of a Wireless MAC Processor over commercial WIFI cards

Settore Scientifico Disciplinare : ING-INF/03

PH.D. CANDIDATE Garlisi Domenico Tutor Ing. Ilenia Tinnirello

COORDINATORE Prof. Ing. Giovanni Garbo

XXIV cycle - 2013/2014

http://wmp.tti.unipa.it

Work carried out under the EU Project FLAVIA

# Abstract

Wireless networks importance for the future Internet is raising at a fast pace as mobile devices increasingly become its entry point. Wireless local area networks are becoming more and more important for providing wideband wireless local access thanks to the impressive success of cheap technologies, such as the IEEE 802.11, working on unlicensed bands. Because of the different application and networking scenarios, several standard extensions have been added to the original 802.11 technology (born as a standard for just cable replacement) with significant standardization efforts. Indeed, wireless service scenarios and application contexts evolve continuously and in an unpredictable way, and require significant and *fast* amendments of the underlying protocols.

In this thesis we face the problem of wireless network programmability as a solution for coping with context-dependent optimizations, moving from one-for-all standard solutions to the concept of programmable wireless interfaces. Although the wireless research and academic community has proposed interesting platforms (e.g. based on Software Defined Radio) for pushing forward dynamic reprogrammability of devices, we argue that it is important to identify a tradeoff between programmability space and usability of the programmable interface.

In this direction, we introduce the concept of Wireless MAC Processor and developed a running prototype over an ultra-cheap wireless card. Wireless MAC processor is a programmable device which provides a set of stateless Medium Access Control commands, and which embeds a MAC protocol engine in charge of executing a finite state machine able to exploit and compose the sequence of commands forming a desired MAC protocol logic. Wireless MAC Processor (WMP) commands can be considered analogous to the instruction set of an ordinary CPU. They are meant to implement elementary actions, namely MAC operations such as transmit a frame, set timers, etc., which may be then executed in the appropriate sequence and/or under the occurrence of specific events and conditions mandated by a protocol logic.

Instead of implementing a specific Medium Access Control (MAC) protocol stack, Wireless MAC processors do support a set of Medium Access Control which can be run-time composed (programmed) through Finite State Machine (FSM), thus providing the desired MAC protocol operation. Flexibility and ease of programmability is thus a consequence of the clear architecture-level decoupling made between what the device is able to do (the pre-installed MAC commands), and what it is instructed at run time, to do (the injected state machine).

The WMP platform has been designed and developed within the European project FLAVIA. The WMP implementation has also been released to the research community, together with a graphical tool for defining and compiling MAC state machines.

In the first chapter of This document we focus the concept of MAC protocol, on the motivation for introducing MAC-level programmability and on the discussion of the state of the art. The second chapter introduce the WMP architecture. We show the elements that compose the WMP and we present the Application Programming Interface, defined in terms of events, conditions and actions available for defining the MAC programs in terms of Extended Finite State Machines (eXtended Finite Sstate Machine (XFSM)). In the third chapter we show the MAC processor implementation details and we discuss some MAC program examples. In chapter four we describe the envisioned API and in chapter five we present the developing tools. In chapter six we explain the implementation of the proposed system over a commodity card (the off-the-shelf Broadcom AirForce54G chipset), by replacing its 802.11 WLAN MAC firmware implementation with our MAC protocol engine. At the end, in chapter seven we present some validation results, where we discuss some real experiments of on-the-fly MAC layer reprogrammability.

In the last chapter, we show as possible add flexibility also other layer, in this case we present **wpa\_fast**, a own framework, developed to add flexibility in the other MAC layer functions. **wpa\_fast** improve the performance for the nodes that work in environments that changing mostly rapidly as vehicular network.

# Acronyms

| AP    | Access Point                         |

|-------|--------------------------------------|

| API   | Application programming interface    |

| BSS   | Basic Service Set                    |

| CCA   | Clear Channel Assessment             |

| CSMA  | Carrier Sense Multiple Access        |

| DCF   | Distribute coordination Function     |

| DCLS  | Direct Channel Link Setup            |

| DHCP  | Dynamic Host Configuration Protocol  |

| DIFS  | DCF Interframe Space                 |

| DL    | Direct Link                          |

| DLS   | Direct Link Setup                    |

| FSM   | Finite State Machine                 |

| GPR   | General Purpose Register             |

| GPT   | General Purpose Timer                |

| IFS   | Interframe Space                     |

| IP    | Internet Protocol                    |

| LLC   | Logical Link Control                 |

| MAC   | Medium Access Control                |

| MCU   | MicroController Unit                 |

| NAV   | Network Allocation Vector            |

| NIC   | Network interface controller         |

| PHY   | Physical layer                       |

| SHM   | SHared Memory                        |

| SPR   | Special Purpose Register             |

| SPROM | Serial Programmable Read Only Memory |

| TDMA  | Time Division Multiple Access        |

| TSF   | Timing Syncronization Function       |

| WMP   | Wireless MAC Processor               |

| XFSM  | eXtended Finite Sstate Machine       |

# Contents

| Ab | strac                           | t 2                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Acro                            | nyms                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1  | 1.1<br>1.2<br>1.3<br>1.4        | ivations: Why MAC flexibility?6The MAC level (link layer)61.1.1 TDMA61.1.2 CSMA/CA71.1.3 Polling MAC9MAC: Why adding flexibility9Flexibility through FSM10State of art111.4.1 Other solutions12MAC flexibility with WMP141.5.1 WMP overview141.5.2 Solutions in comparison14                                                                                                                                  |

| 2  | The<br>2.1<br>2.2<br>2.3        | Wireless MAC Processor16Introduction16Elements of a FSM16The WMP concept182.3.1WMP architecture202.3.2WMP development tool202.3.3WMP implementation on wireless card overview21                                                                                                                                                                                                                               |

| 3  | 3.1<br>3.2<br>3.3<br>3.4        | P Architecture22General WMP Architecture22The MAC-Engine25WMP API introduction26Byte-Code263.4.1 Structure of the Byte-Code273.4.2 Byte-Code of the DCF State Machine30WMP platform33Binary-Byte-Code343.6.1 States region343.6.2 Transitions region363.6.3 State parameters region37                                                                                                                         |

| 4  | <b>API</b><br>4.1<br>4.2<br>4.3 | details: events, conditions and actions38State parameters40Events414.2.1Events to handle the TX424.2.2Events to handle the RX424.2.3Events to handle the timer42Conditions434.3.1Conditions to handle the RX434.3.2Conditions to handle the RX434.3.3Conditions to handle the timer434.3.4Conditions to handle the timer434.3.4Conditions to handle the timer434.3.4Conditions to handle the timer44Actions44 |

|   |      | 4.4.1Actions to handle the TX444.4.2Actions to handle the RX454.4.3Actions to handle the timer454.4.4Actions to handle the parameters46 |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 5 |      | P Development Tool 48                                                                                                                   |

|   | 5.1  | WMP-Editor                                                                                                                              |

|   |      | 5.1.1 WMP-Editor element description 49                                                                                                 |

|   |      | 5.1.2 WMP-Editor to define a MAC protocol 49                                                                                            |

|   |      | From a model to a Binary-Byte-Code 54                                                                                                   |

|   | 5.3  | Byte-Code-Manager    55                                                                                                                 |

|   |      | 5.3.1 Byte-Code injection and activation 55                                                                                             |

|   |      | 5.3.2 Delayed Byte-Code switching 59                                                                                                    |

|   |      | 5.3.3 Debugging options                                                                                                                 |

|   |      | 5.3.4 Forge control frame                                                                                                               |

| 6 | WM   | P implementation on commodity hardware 62                                                                                               |

|   | 6.1  | Introduction                                                                                                                            |

|   | 6.2  | The Hardware Platform AirForce54G                                                                                                       |

|   |      | 6.2.1 Platform : registers, memory addressing and subroutine system 64                                                                  |

|   |      | 6.2.1.1 Special Purpose Register (SPR)                                                                                                  |

|   |      | 6.2.1.2 Conditional registers                                                                                                           |

|   |      | 6.2.2 Development tools                                                                                                                 |

|   | 6.3  | WMP Implementation                                                                                                                      |

|   |      | 1                                                                                                                                       |

| 7 | MAC  | C design and evaluation 70                                                                                                              |

|   | 7.1  | Design Overview                                                                                                                         |

|   | 7.2  | Distributed Coordination Functions (DCF)                                                                                                |

|   |      | 7.2.1 DCF programmability                                                                                                               |

|   |      | 7.2.2 DCF with Access Point feature                                                                                                     |

|   |      | 7.2.3 DCF Experimental Results                                                                                                          |

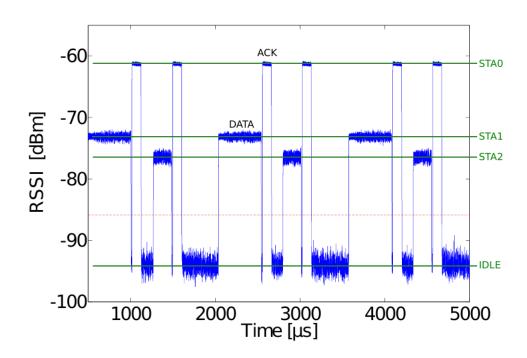

|   | 7.3  | Time Division Multiple Access (TDMA)    75                                                                                              |

|   |      | 7.3.1 TDM Experimental Results                                                                                                          |

|   | 7.4  | Direct Link                                                                                                                             |

|   |      | 7.4.1 State parameter in D(C)LS                                                                                                         |

|   |      | 7.4.2 DLS and DCLS performance evaluation                                                                                               |

|   | 7.5  | Power consumption evaluation                                                                                                            |

| 8 | Higł | a level flexibility 84                                                                                                                  |

| - |      | Introduction                                                                                                                            |

|   | 8.2  | Vehicular network                                                                                                                       |

|   |      | WLANs Association Schema                                                                                                                |

|   |      | 8.3.1 MAC level functionality                                                                                                           |

|   |      | 8.3.2 Network level functionality                                                                                                       |

|   | 8.4  | WPA FAST to improve the time connection se-tup                                                                                          |

|   | 8.5  | WPA FAST implementation                                                                                                                 |

|   | 8.6  | Testebed set-up                                                                                                                         |

|   | 8.7  | Experimental evaluation                                                                                                                 |

| • |      |                                                                                                                                         |

| A |      | endix<br>Hardware Deployment                                                                                                            |

|   |      | Hardware Deployment    94      References and link    94                                                                                |

|   | പ.പ  | пененско ани шик                                                                                                                        |

# Chapter 1

# Motivations: Why MAC flexibility?

### 1.1 The MAC level (link layer)

In the seven-layer OSI model of computer networking, media access control (MAC) data communication protocol is a sublayer of the data link layer. The MAC sublayer provides addressing and channel access control mechanisms that make it possible for several terminals or network nodes to communicate within a multiple access network that incorporates a shared medium, e.g. Wireless [2].

The MAC sublayer acts as an interface between the logical link control (LLC) sublayer and the network's physical layer. The MAC layer emulates a full-duplex logical communication channel in a multi-point network. This channel may provide unicast, multicast or broadcast communication service.

A channel access mechanism is the part of the protocol which specifies how the node uses the medium (when to listen, when to transmit) and how it coexists with the other nodes belonging to the same network. In the next section we report same example of MAC, in detail we describe Time Division Multiple Access (TDMA), Carrier Sense Multiple Access (CSMA) and Polling which are the 3 main classes of channel access mechanisms for radio.

#### 1.1.1 TDMA

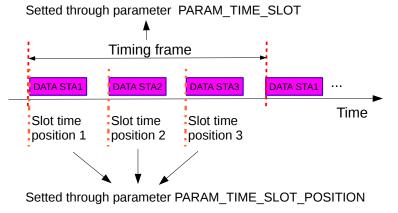

TDMA (Time Division Multiplex Access) is very simple. A specific node, the base station, has the responsibility to coordinate the nodes of the network. The time on the channel is divided into time slots, which are generally of fixed size. Each node of the network is allocated a certain number of slots where it can transmit. Slots are usually organised in a frame, which is repeated on a regular basis [4].

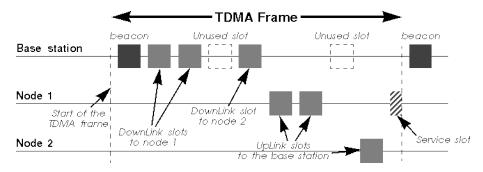

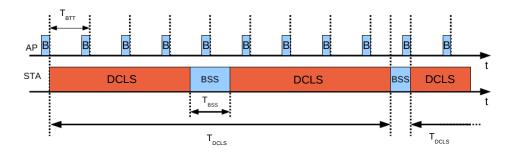

The base station specifies in the beacon (a management frame) the organisation of the frame. Each node just needs to follow blindly the instructions of the base station. Very often, the frame is organised as downlink (base station to node) and uplink (node to base station) slots, and all the communications go through the base station. A service slot allows a node to request the allocation of a connection, by sending a connection request message in it. In some standards, uplink and downlink frames are one different frequencies, and the service slots might also be on a separate channel. The figure 1.1 summarizes a typical scenario of TDMA MAC protocol with a base station and two nodes, which highlights the slots of the nodes, but also the frame.

Figure 1.1: TDM MAC

TDMA suits very well CBR applications, such as voice calls, because those application have very predictable needs (fixed and identical bit rate). Each handset is allocated a downlink and a uplink slot of a fixed size (the size of the voice data for the duration of the frame). For these reasons TDMA is used into several cellular phone standards (GSM in Europe, TDMA and PCS in the USA) and cordless phone standards (DECT in Europe). TDMA is also very good to achieve low latency and provide bandwidth guarantees.

TDMA is not well suited for data networking applications, because it is very strict and inflexible. IP is connectionless and generates bursty traffic which is very unpredictable by nature, while TDMA is connection oriented (so there are some overheads for creating connections for single IP packets). TDMA use fixed size packets and usually symmetrical link, which doesn't suit IP that well (variable size packets).

TDMA performance are strongly affected by the interference conditions experienced on the allocated frequency band. In a dedicated clean band, as it is the case for cellular phone standard, TDMA is fine. Conversely, in unlincensed bands, because it does not explicitly take into account interference created by other networks, TDMA performance can be critical.

#### 1.1.2 CSMA/CA

CSMA/CA (Carrier Sense Multiple Access/Collision Avoidance) is the channel access mechanism used by most wireless LANs in the ISM bands.

The basic principles of CSMA/CA are listen before talk and contention. This is an asynchronous message passing mechanism (connectionless), delivering a best effort service, but no bandwidth and latency guarantee. The protocol is very suitable for data bursty applications and is quite robust against interferences.

CSMA/CA is fundamentally different from the channel access mechanism used by cellular phone systems.

CSMA/CA is derived from CSMA/CD (Collision Detection), which is the base of Ethernet. The main difference is the collision avoidance: on a wire, the transceiver has the ability to listen while transmitting and so to detect collisions (with a wire all transmissions have approximately the same power). But, even if a radio node could listen on the channel while transmitting, the power of its own transmissions would mask all other signals on the air. So, the protocol can't directly detect collisions and only tries to avoid them.

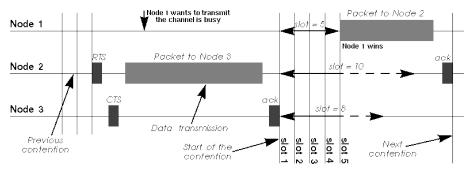

Figure 1.2: CSMA MAC

The protocol starts by listening on the channel (this is called carrier sense), and if it is found to be idle, it sends the first packet in the transmit queue. If it is busy (either another node transmission or interference), the node waits the end of the current transmission and then starts the contention (wait a random amount of time). When its contention timer expires, if the channel is still idle, the node sends the packet. The node having chosen the shortest contention delay wins and transmits its packet. The other nodes just wait for the next contention (at the end of this packet). Because the contention is a random number and done for every packets, each node is given an equal chance to access the channel (on average - it is statistic). The figure 1.2 shows a typical scenario of CSMA/CA with three nodes, the node two transmit after a RTS/CTS procedure, in the RTS/CTS (Request to Send / Clear to Send) procedure, two little frame are exchange between the nodes, before the real frame, to reduce frame collisions introduced by the hidden node problem. The node 1 in figure 1.2, win the contention procedure because it extracts a period of 5 slot before to start the frame transmit, node 2 extracts 10 and node 3 extracts 8.

As we have mentioned, we can't detect collisions on the radio, and because the radio needs time to switch from receive to transmit, this contention is usually slotted (a transmission may start

only at the beginning of a slot : 9  $\mu$ s in 802.11g ). This makes the average contention delay larger, but reduces significantly the collisions (we can't totally avoid them).

**The basic IEEE 802.11 MAC layer** uses the distributed coordination function (DCF) to share the medium between multiple stations. (DCF) relies on CSMA/CA and optional 802.11 RTS/CTS to share the medium between stations [20]. DCF employs a CSMA/CA with binary exponential backoff algorithm.

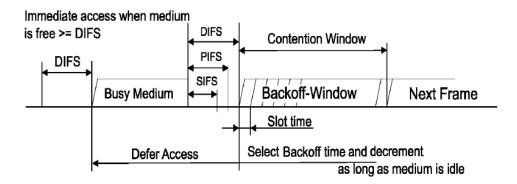

The time interval between frames is called the Interframe Space (IFS). A STA shall determine that the medium is idle through the use of the CS function for the interval specified. Five different IFSs are defined to provide priority levels for access to the wireless media. Figure 1.3 shows some of these relationships.

- SIFS short interframe space

- PIFS PCF interframe space

- DIFS DCF interframe space

- AIFS arbitration interframe space (used by the QoS facility)

- EIFS extended interframe space

DCF requires a station wishing to transmit to listen for the channel status for a precise interval time, named DCF Interframe Space (DIFS). If the channel is found busy during the DIFS interval, the station defers its transmission. In a network where a number of stations contend for the wireless medium, if multiple stations sense the channel busy and defer their access, they will also virtually simultaneously find that the channel is released and then try to seize the channel. As a result, collisions may occur. In order to avoid such collisions, DCF also specifies random backoff, which forces a station to defer its access to the channel for an extra period.

The different IFSs shall be independent of the STA bit rate. The IFS timings are defined as time gaps on the medium, and the IFS timings except AIFS are fixed for each PHY (even in multirate-capable PHYs). The IFS values are determined from attributes specified by the PHY.

This figure 1.3 gives description of DCF on a time scale as shown below. As we see when a STA becomes ready to transmit it senses the medium for a period of DIFS. If it senses that the medium was busy during this interval, the STA defers transmission to later time that depends on the backoff time. The backoff time is calculated using the following relationship

BackoffTime = Random() \* aSlotTime

Random() is a value in the interval [0, CW], where CW take a value between aCWmin and aCWmax i.e. aCWmin < CW < aCWmax. The values of aCWmin and aCWmax are defined for PHY. Value of CW is incremented exponentially as shown below. Value for inter frame space are different for different standard, the table 1.1 report a detail parameter for main IEEE WIFI standards.

Figure 1.3: Inter Frame Space in 802.11 standards

| Parameters          | 802.11b (HR/DSS) | 802.11g(OFDM)                | 80211.a (OFDM) |

|---------------------|------------------|------------------------------|----------------|

| slottime            | $20\mu$          | 9μ                           | <b>9</b> $\mu$ |

| SIFS                | 10 $\mu$         | $16\mu$                      | $16\mu$        |

| PIFS                |                  | $SIFS + t_{slot}$            |                |

| DIFS                |                  | $SIFS + (2 \times t_{slot})$ |                |

| Operating Frequenzy | 2.4GHz           | 2.4GHz                       | 5GHz           |

| Maximum Data Rate   | 11Mbps           | 54Mbps                       | 54Mbps         |

| CWmin               | 31               | 15                           | 15             |

| CWmax               | 1023             | 1023                         | 1023           |

Table 1.1: IEEE 802.11 parameters

#### 1.1.3 Polling MAC

Polling is the third major channel access mechanism, after TDMA and CSMA/CA. The most successful networking standard using polling is 100vg (IEEE 802.12), but some wireless standard are also using it. For example, 802.11 offers a polling channel access mechanism (Point Coordination Function) in addition to the CSMA/CA one, that has been improved in the 802.11e extensions under the name of HCCA.

Polling is in fact in between TDMA and CSMA/CA. The base station retains total control over the channel, but the frame content is no more fixed, allowing variable size packets to be sent. The base station sends a specific packet (a poll packet) to trigger the transmission by the node. The node just waits to receive a poll packet, and upon reception sends what it has to transmit.

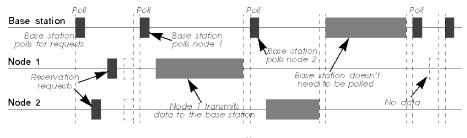

Polling can be implemented as a connection oriented service (very much like TDMA, but with higher flexibility in packet size and resource allocation) or connection less-service (asynchronous packet based). The base station can either poll permanently all the nodes of the network just to check if they have something to send (that is workable only with a very limited number of nodes), or the protocol use reservation slots where each node can request a connection or to transmit a packet (depending is the MAC protocol is connection oriented or not). The figure 1.4 shows an example of MAC polling with a base station and two node, any nodes transmit only after the poll frame sended by base station.

Figure 1.4: Polling MAC

In the case of 100vg, the polling mechanism doesn't use any bandwidth (it's done out of band through tones), leading to a very efficient use of the channel (over 96% user throughput). For 802.11 and wireless LAN, all the polling packets have to be transmitted over the air, generating much more overhead. More recent system use reservation slots, which is more flexible but still require significant overhead.

As CSMA/CA offers ad-hoc networking (no need of a base station) and similar performance, it is usually preferred in most wireless LANs. For example, most 802.11 vendors prefer to use the distributed mode (CSMA/CA) over the coordinated mode (polling).

### **1.2 MAC: Why adding flexibility**

More than 20 years have elapsed since the establishment, in 1990, of the IEEE 802.11 Wireless Local Area Network committee. Initially foreseen as a technology for replacing Ethernet cables with wireless connectivity, IEEE 802.11 has been severely challenged by the highly heterogeneous needs emerged in the last two decades. Indeed, the original 802.11 CSMA/CA Medium Access Control (MAC) has shown significant shortcomings when facing the breakthrough rate improvements

made available by the latest PHY enhancements (802.11n, 802.11ac), as well as when applied to scenarios and contexts such as ad hoc and mesh networks, vehicular environments, directional antennas, quality of service support, real time media streaming support, multi-channel operation, dynamic spectrum access, and many others [5].

Actually, the WLAN research community has found effective and ingenious solutions for adapting the 802.11 MAC operation to these new challenges. However, as for instance detailed in a comprehensive analysis carried out in the frame of the FLAVIA FP7 European project [18], **most of the proposed MAC modifications do not comply with the 802.11 standard MAC operation**. In the best case, i.e. when the required MAC amendments are endorsed by some 802.11 standardization task groups, several years may elapse before they become available in commercial cards/devices. More frequently, when the promoted MAC amendments are either deemed out of the standard task groups scope, or mandate a way too significant departure from the native CS-MA/CA MAC operation, their real world deployment is very unlikely, especially when they require changes in time-critical operations natively implemented in the network interface card.

Therefore, we need flexibility in MAC developing and maintenance. In order to insert flexibility when realize a MAC protocol, we need a model of the MAC protocol that optimize the development and maintenance. Therefore, a good modeling and abstraction method is essential, since it can significantly improve the quality and efficiency of the MAC. Another aspect that drives the development of MAC abstraction mechanisms is the ease-of-use and the degree of comfort that can be provided during the implementation and maintenance of it. One way to achieve this is to use a FSM to model the MAC.

### **1.3 Flexibility through FSM**

A finite-state machine (FSM) is a mathematical model of computation used to design both computer programs and sequential logic circuits. It is conceived as an abstract machine that can be in one of a finite number of states. The machine is in only one state at a time; the state it is in at any given time is called the current state. It can change from one state to another when initiated by a triggering event or condition; this is called a transition, a action can be execute when a transition is called. A particular FSM is defined by a list of its states, and the triggering condition for each transition[3].

The behavior of state machines can be observed in many devices in modern society which perform a predetermined sequence of actions depending on a sequence of events with which they are presented. Simple examples are vending machines which dispense products when the proper combination of coins is deposited, elevators which drop riders off at upper floors before going down, traffic lights which change sequence when cars are waiting, and combination locks which require the input of combination numbers in the proper order.

Finite-state machines can model a large number of problems, among which are electronic design automation, communication protocol design, language parsing and other engineering applications. In biology and artificial intelligence research, state machines or hierarchies of state machines have been used to describe neurological systems and in linguistics to describe the grammars of natural languages.

Figure 1.5 shows the parts of a finite state machine. The circles represent states. The arcs represent the transitions from one state to another. Each arc label is a condition. The slashes separate actions.

The proposed design approach, to realize a MAC protocol, is based on the finite state machine (FSM) mechanism. This mechanism fits the periodic structure of typical MAC applications. Thus, the transfer of a theoretical system description into a software implementation is easy to realize. Moreover, the FSM based abstraction makes it easier to split an algorithm into short segments (i.e. states), which can be developed and tested separately.

In order to improve the development process of MAC protocol programming and to handle the growing complexity of devices, different programming abstraction methods have been introduced. But, since each abstraction method brings certain advantages and drawbacks, developers often have to make a tradeoff between ease-of-use and efficiency, when selecting a programming mechanism[10]. Programming abstraction methods can be classified by a set of qualitative and quantitative parameters, which help developers to select an abstraction method that best fits their application. These parameters are Usability, Readability, Modularity, Reliability and Efficiency.

Modeling and abstraction methods should satisfy the following aspects, in order to bring an advantage during the software design and implementation process.

Figure 1.5: State machine example

- 1. Usability: A software abstraction method should help designers to formulate a real world problem in a standardized syntax. The syntax and code-structure should therefore be designed in such a manner that it is able to support a developer in understanding and formulating the problem at hand in a simple and time-efficient manner.

- 2. Readability: Enforcing a good software structure, the abstraction method can improve the readability of the resulting source code and therefore assists in the prevention of code errors.

- 3. Reliability: A good software abstraction method can help to detect and prevent invalid system behavior as soon as possible in the development process. Hence the embedded software can be implemented in such a way that it is possible to avoid a system lock-up or that it is possible for the system perform to an automatic recovery from invalid system states and lock-up conditions.

- 4. Efficiency: In order to make the best use of available resources, the generated code should have a small memory footprint and should create minimal runtime overhead.

An abstraction method, which very well fulfills the parameters mentioned previously, is the FSM mechanism, the idea is to use this method to develop the MAC protocol. Thus, the WMP architecture introduced in this thesis uses finite state machines as its basic working principle [10]. The following application examples emphasize the benefits to use FSM in WLAN applications.

- Flexible WLAN Applications: Wireless nodes often have to switch the currently running software according to the application scenario in which they are used. In sensor networks that rely on a dynamic mesh or a clustered topology the node must be capable of adapting to changes in the topology. In the that the system can handle different application scenarios and can provide different services, without requiring a modification of the hard software. No context switching between software modules is needed and so a full-scale real-time operating system, that comes with an enormous memory overhead, is not required. An FSM based implementation is well suited for these scenarios, since a top-level FSM can be used to select the required application, which is realized as a subFSM.

- Module Splitting: With the growing complexity of wireless applications, the embedded software used to run the systems becomes more advanced. In order to handle the system's complexity it is a common design practice to split an MAC protocol into sub modules, which can then be implemented and can be more easily maintained. In general these modules can be implemented as a sub-state machine and they are then called by the top-level FSM. Since the modules interact via well defined interfaces the different modules are interchangeable and can easily be reused.

### 1.4 State of art

A very first step to address the above concerns is to evolve from the current generation of closed network interface cards, implementing the very specific WLAN protocol stack, to programmable

WLAN platforms, capable of permitting software-based modifications in the wireless access operation. Obviously, the technical hurdle to face is how to support or modify time-critical operations which cannot be delegated to driver-level software modification, or controlled by dedicated overlay software modules running on the host computer [5].

The ability to modify the operation of commodity WLAN systems goes along with the availability of public-domain open-source 802.11 MAC protocol code. Besides the significant expertise required to modify existing code, a further deployment barrier for many appealing MAC extensions consists in the limited extent to which software changes may affect the device operation. Indeed, early 802.11 devices were designed according to a full-MAC approach. The MAC layer was almost entirely implemented in the card hardware/firmware, and programmability of the relevant drivers (when provided as open source) involved a marginal set of functionalities.

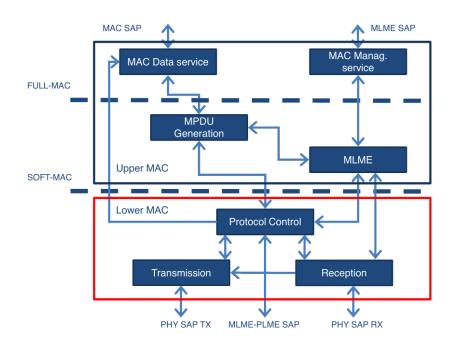

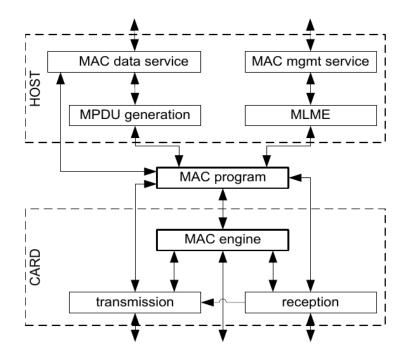

The flexibility of commodity WLAN cards has significantly improved since a number of vendors (including Intel, Ralink, Realtek, Atheros, Broadcom), started to exploit an innovative soft-MAC [22] design, transferring to the host processor non-time-critical MAC layer functionalities (figure 1.6).

Figure 1.6: WLAN MAC architectures: PHY full-MAC vs soft-MAC.

Still, even in the soft-MAC case, the "Lower MAC", comprising crucial sub-systems such as transmission, reception and protocol control, remains hard-coded in the card.

#### 1.4.1 Other solutions

Some chipsets (e.g. from Atheros and Broadcom) permit the tuning of selected MAC parameters (such as contention windows) via registers, more substantial MAC operation changes require access to the firmware code [5]. To the best of our knowledge, no vendor has to date released an open source firmware, and the only available public-domain code is OpenFWWF [14], a recently released simplified DCF firmware implementation for Broadcom/AirForce chipsets. However, OpenFWWF extensions require reimplementation of large portions of assembly code, thus making it usable only by experts.

In parallel, a significant effort has been spent on the development of overlay software modules. Solutions such as the Overlay MAC Project [23], MultiMAC [24], FlexMAC [25], Soft-TDMAC [26], etc, do exploit firmware configuration registers and some driver hacks for building quite advanced MAC programming interface (for instance, MultiMAC permits to override the frame format, disable ACKs, RTS/CTS, virtual carrier sense, disable transmission backoff, etc).

Even if notable implementations of custom MAC protocols, including TDMA-like ones, have been demonstrated, overlay approaches cannot get rid of some intrinsic limitations. Their scalability may be impaired by the need to overlap and duplicate similar functionalities at different layers; they remain constrained by the basic programming interface made available by the driver; and their limited ability to accurately control the card's timing prevents to deploy features such as programmable management of frame replies and handshakes, precise scheduling of medium access times, fine-grained radio tuning control, etc.

The research community has mainly circumvented this issue by developing FPGA-based and/or Software Defined Radio platforms, such as [29], [30], [12], [13], [31], [27], [16], and has therein implemented and tested modifications to the wireless access operation.

Clearly, the shift from commodity wireless cards to dedicated wireless platforms permits to push programmability much farther, although the beneficiaries remain mainly confined within the research community - real world deployment of costly and/or bulky platforms being unlikely.

Early platforms such as CalRadio [29] reimplemented the 802.11 MAC protocol stack on, respectively, a Xilinx FPGA and a Texas DSP, interfaced to a commercial PHY-only Intersil 802.11b chip. As such, they permitted arbitrary MAC modifications, but protocol reconfiguration required a deep knowledge of the platforms and could only be done offline by recompiling the modified C code.

Software defined radio (SDR) platforms, such as GNURadio [12] and USRP [13], overcome the dependency on a specific PHY interface and permit to develop full-custom MAC/PHY cross-layer protocols. A large amount of work focuses on means to improve the slow SDR performance. On one side, solutions such as SORA [31] achieve a throughput comparable to commodity 802.11 hardware by distributing computation on multiple cores and by relying on sophisticated optimizations, as well as on an efficient radio control board. However, the software complexity makes protocol stack modifications not easy, as any update implies a redesign of the software block repartitions to multiple CPU cores.

On the other side, platforms such as WARP [16] and AirBlue [27] improve performance by delegating most processing functions to the FPGA Hardware, meanwhile retaining the ability to closely control such functions via, e.g., registration of interrupt handlers, hardware triggers, read/write of hardware registers, etc. In the case of AirBlue, a modular organization coupled with careful design choices permits relatively easy modifications, changes in a module not affecting the others.

[32] and [33] start from a "breakdown" analysis devised to identify core MAC functions. Based on this, [32] proposes a split functionality architecture, where time-critical MAC functions are run on the radio hardware, but their control is kept on the host PC. The architecture is implemented over the GNURadio and USRP SDR platforms. Conversely, in the Decomposable MAC framework proposed in [33] and detailed in [34] both basic blocks and protocol logic are supported on a WARP platform. The MAC protocol is composed via a wiring engine which connects the basic blocks required to support the desired MAC operation.

The solution proposed in [33] uses MAC functions and support the MAC protocol logic directly on the radio card.

Different implementations of wireless systems used the concept of finite state machines. An over-the-air reprogramming protocol based on a state machine model is presented in [35]. In [36] a mechanism to derive a FSM based graphical description from existent TinyOS applications was designed. This approach is only usable for debugging purposes and does not improve the implementation or development process. Another approach is presented in [37], in which a state machine runtime environment has been implemented as a TinyOS component. This approach is rather simple and does not consider a hierarchical software structure. Hence the system is not usable in more complex applications [10].

Kasten and Römer introduced the OSM programming language and model, used to describe hierarchical and parallel finite state machines in [40]. The state flow is described using OSM code, which is, at a later stage, compiled into native C code. State and event functions, on the other hand, are directly implemented in C. An experimental OSM compiler was developed, but until now no full tool-chain has been published.

The Quantum framework [38] implements state machines based on an object oriented software framework in C++. The implementation realizes the state-flow by calling the different state handlers via a single function pointer. However, because the quantum framework enables parallel code execution, it requires a complex event posting and distribution mechanism.

The SenOS operating system [39] provides a runtime environment for a finite state machine based application development. The system kernel consists of a state sequencing and event queuing mechanism. But, instead of defining an application layer, each state directly enables a driver function in the callback library of the system.

## 1.5 MAC flexibility with WMP

#### 1.5.1 WMP overview

The **Wireless MAC Processor (WMP)** is an architecture platform devised to run a wireless MAC program defined in terms of a **Finite State Machine (FSM)**, The WMP can be implemented on commodity hardware. The main element of WMP are: an execute finite state machine that named MAC-Engine and space memory to store 2 Binary-Byte-Code, the Binary-Byte-Code is a textual description of a FSM o MAC-Program [8]. It has been shown, in fact, that MAC protocols can be described in terms of state machines made of three main elements: actions, events and conditions.

In the WMP case, actions are commands for the radio hardware, such as transmit a frame, set a timer, and switch to a different frequency channel. Events include hardware interrupts such as channel up/down signals, indication of reception of specific frame types, expiration of timers and so on. Conditions are boolean expressions evaluated on internal configuration registers that can either explicitly updated by actions, or implicitly updated by events. Some registers are store general MAC layer information (like the current radio channel or the power level), or more specific MAC variables (like the contention window value and the backoff parameter).

Starting from an initial (default) state, the WMP waits for events which trigger state transitions. The actual transition can be enabled or disabled by verifying a boolean condition, while an action on the hardware system (i.e. on the transreceiver) can be performed before completing the transition to the new state.

We implemented the WMP on commercial card Broadcom AirForce54G to test the feasibility of the proposed solution, we obtain a proof of concept that good work and we use it to performance several experiment with different MAC protocol and different environment set-up.

#### 1.5.2 Solutions in comparison

We clearly distinguish from related work in the previous section, unlike other works which rely on dedicated DSPs or programmable hardware platforms, we experimentally prove the feasibility of the wireless MAC processor concept over ultracheap commodity WLAN hardware cards. Specifically, we reflash the firmware of the commercial Broadcom AirForce54G off-the-shelf chipset, **replacing its** 802.11 WLAN MAC protocol implementation with our proposed extended **state machine execution engine**.

For these reasons, the WMP differs from off-the-shelf wireless NICs powered with their "vanilla" code: while the latter are tied to a specific MAC protocol (i.e., IEEE 802.11), the WMP architecture can run generic FSM, hence it can implement users' designed MAC programs. On the basis of a predefined (hardware-dependent) set of actions, events and conditions which represent the platform API, a MAC programmer can easily compose different channel operations into a MAC program and execute it on the WMP.

[32] and [33] are probably the works more closely related to the Wireless MAC Processor approach presented in this thesis. Both start from a "breakdown" analysis devised to identify core MAC functions. The architecture is implemented over the GNURadio and USRP SDR platforms. The MAC protocol is composed via a wiring engine which connects the basic blocks required to support the desired MAC operation [5].

Similar to [33], we also support the MAC protocol logic directly on the radio card. However, our work differs from [32], [33] for at least three major aspects.

- Our breakdown analysis further includes events and conditions, in addition to MAC functions.

- We leverage injection in the radio hardware (and more specifically in the designed MAC protocol engine) of Extended Finite State Machines, thus permitting a greater flexibility as well as run-time re-programmability of the MAC operation without interrupting the MAC service.

- We rely on resource-constrained commodity WLAN cards instead of powerful and capable FPGA radio boards.

The WMP approach represents a major R&D leap from related work in this area since, unlike other works which rely on dedicated DSPs or programmable hardware platforms, we will experimentally prove:

- The feasibility of the wireless MAC processor concept over ultra-cheap commodity WLAN hardware cards.

- The possibility of programming time-critical medium access operations and event triggered PHY configurations without knowing any detail about the internal design of the hardware platform.

# Chapter 2

# **The Wireless MAC Processor**

## 2.1 Introduction

The **Wireless MAC Processor (WMP)** is a Finite State Machine (FSM) executor that runs inside a wireless Network interface controller (NIC): having direct access to the underlying hardware functions of the NIC, Radio, PHY and other facilities like timers, the finite state machine running in the WMP can be tailored to mimic a full featured Medium Access Control algorithm. This is achieved by exposing to the WMP a number of basic elements directly connected to the hardware, such as signaling from the Radio and the PHY that reports incoming frames from the air, and a few elementary actions, like frame passing to/from the radio. This approach shows many improvements with respect to classic implementations:

- Users can easily define new MACs by composing finite state machines using a graphical tool: thanks to a drag and drop interface, simple operations like frame sending or ack waiting can be composed into a complex MAC;

- Existing MAC can be easily modified/updated;

- Different MACs can be used in the same machine, either they can be selected for independent execution or they can coexist in the WMP at the same time and periodically activated (virtualization).

## 2.2 Elements of a FSM

A finite state machine is a model of a reactive system. The model defines a finite set of states and behaviour and how the system transitions from one state to another when certain events are triggered and conditions are true. Finite state machines are used to model complex logic in dynamic systems, from automatic transmissions to robotic systems to mobile phones. Examples of this complex logic include:

- Scheduling a sequence of tasks or steps for a system

- Defining fault detection, isolation, and recovery logic

- Supervising how to switch between different modes of operation

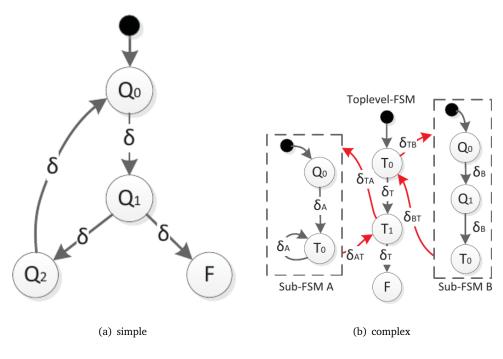

The formalism known as the finite state machine describes sequential logical systems and is frequently applied to describe algorithms in computer science, as well as to design digital electronic circuits. As previously mentioned, wireless systems can be implemented using FSM based design approaches [10]. A typical FSM (see 2.1) can either be represented graphically using state-charts [41] or can be formulated using a mathematical description [42] based on an 5-tuple that combines the following elements:  $(\Sigma, Q, q0, \delta, F)$

- $\Sigma$  Input Alphabet (finite set of valid input events)

- Q Set of System-States

- q0 Initial State q0  $\epsilon$  Q

- $\delta$  Transition function  $\delta : \mathbf{Q} \times \Sigma \rightarrow \mathbf{Q}$

Figure 2.1: FSM

• F Set of Final States  $F \subseteq Q$

A hierarchical finite state machine, (see Figure 2.1) is a concept used to split large state machine definitions into sub-modules. The mathematical description can represent this splitting by describing the entire state machine as a set of sub-state machines Mhierarchical = {  $M_0$  ,  $M_1$ ,  $M_N$  } defines the system's top-level module, which contains the application's first entry point after the start-up. The 7-tuple ( $\Sigma$ , Q, q0, F, T,  $\delta$ ,  $\Sigma_s ub$ ) is derived from the description for non-hierarchical state machines. As can be seen below, every sub-FSM has to define a set of states that allow a transition and re-entry from and to other sub-state machines. Furthermore, a transition function which describes the program-flow between sub-state machines has to be defined.

- T States that allow entry/re-entry  $T\subseteq Q$

- $\Sigma_{sub}$  Transitions to sub-FSM  $\Sigma_{sub} : T_n \ge \Sigma_M$

Hierarchical finite state machines can be applied in various wireless systems that require a complex system architecture. These systems often consist of multiple independent sub-modules, which have to interact via several well defined interfaces. An other form of state machine are the extended finite state machine, in a conventional finite state machine, the transition is associated with a set of input Boolean conditions and a set of output Boolean functions. In an extended finite state machine (XFSM) model, the transition can be expressed by an "if statement" consisting of a set of trigger conditions. If trigger conditions are all satisfied, the transition is fired, bringing the machine from the current state to the next state and performing the specified data operations. How explained in the section 2.3, the definition of the MAC logic in terms of extended finite state machines (XFSM) permits to control the actions executed by the hardware, for this reason we use this type to model the MAC protocol. The following application examples emphasize the benefits of FSMs in wireless applications.

**Wireless Applications** : Wireless system nodes often have to switch the currently running software according to the application scenario in which they are used. In wireless networks that rely on a dynamic mesh or a clustered topology the node must be capable of adapting to changes in the topology. In the design of end-user devices it is mandatory that the system can handle different application scenarios and can provide different services, without requiring a modification of the

embedded software. In this kind of system, several application modules exist in parallel in the MicroController Unit (MCU) memory but just one module is enabled at a time. Hence, no context switching between software modules is needed and so a full-scale real-time operating system, that comes with an enormous memory overhead, is not required. An HFSM based implementation is well suited for these scenarios, since a top-level FSM can be used to select the required application module, which is realized as a sub-FSM.

**Module Splitting** : With the growing complexity of wireless applications, the software used to run the systems becomes more advanced. In order to handle the system's complexity it is a common design practice to split an application into sub modules, which can then be implemented and can be more easily maintained. However due to the strong coupling between different segments in a typical embedded application it can be difficult to realize this kind of module splitting efficiently. An application based on a hierarchical state machine enables efficient module splitting in the different hardware abstraction layers, while avoiding the additional overhead of a full real-time kernel. A wireless system application. These modules can be implemented as a sub-state machine and they are then called by the top-level FSM. Since the modules interact via well defined interfaces the different modules are interchangeable and can easily be reused.

**Driver Implementation** : Additionally to the application layer, it can also be a good option to implement device drivers in the form of a state machine. Radio modules or intelligent sensor modules often require to trigger an interaction and then utilize the MCU to process the module's response, a behaviour which fits the FSM abstraction very well.

## 2.3 The WMP concept

For abstracting the hardware capabilities and defining hardware agnostic programs to be injected into the wireless cards, the WMP architecture implements a state machine execution engine, called the MAC engine, and a set of elementary actions and signals directly on the card. The MAC engine is an executor of MAC programs, (specified in terms of a high-level state machine) that can be ported on different card systems. The definition of the MAC logic in terms of extended finite state machines (XFSM) permits to control the actions executed by the hardware. The MAC protocol logic defines the medium access behavior whose evolution depends on events (frame arrivals, timer expiration, etc.) and condition verification on configuration registers [11]. The set of events generated and/or revealed by the card hardware, the set of actions coded in terms of predefined firmware modules, and the set of card registers whose settings can be tuned and verified represent the device API that cannot be modified by the user.

The proposed system architecture can be considered analogous to the instruction set of an ordinary CPU. They are meant to implement elementary actions, namely MAC operations such as transmit a frame, set a timer, freeze a backoff, etc, which may (or may not) be then executed in the appropriate sequence and/or under the occurrence of specific events and conditions mandated by a protocol logic. Going ahead with the same analogy, the MAC protocol engine can be somewhat related to an ordinary CPU control unit. It is in charge of executing an user-developed software program implementing the desired MAC protocol operation, which, in our proposed architecture, is provided in the form of an extended finite state machine. Flexibility and ease of programmability is thus a consequence of the clear architecture-level decoupling made between what the device is able to do (the pre-installed MAC commands), and what it is instructed - at run time - to do (the injected state machine). We describe the extended finite state machine through **events**, **conditions**, and **actions**. The theoretical approach followed in the realization of the WMP is that of a FSM with essentials like states and transitions enriched with three additional elements, namely events, conditions and actions that improve the flexibility of the resulting system. We report in chapter 4 all the elements that can be used define several different MAC programs.

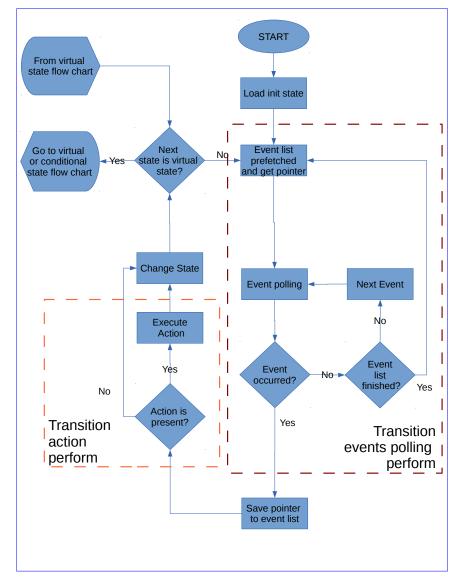

MACs defined for the WMP can be considered following two abstraction layers: a textual one, where everything is described using text expressions, and a graphical one, where the state machine is described through a practical graph based approach. The former representation is the **Byte-Code**, a text file that can be either written at hand by users, or automatically generated by the **WMP-Editor**, a graphical tool that can be used to build the latter representation. This tool helps users composing new FSM, elements can be, in fact, connected together thanks to a straightforward drag and drop interface: furthermore it also checks for semantic errors during the design phase

and for this reason it is strongly recommended to use it and avoid to manually write a Byte-Code. The code isn't compiled but it is interpreted from MAC-Engine. The software for pushing the code to the MAC is called **Byte-Code-Manager**.

The Wireless MAC Processor architecture somewhat mimics the organization of ordinary computing systems [6], where programmability is accomplished by specifying

- an adequate instruction set which permit to perform elementary tasks on a machine;

- a programming language which conveys multiple instructions (suitably assembled to implement a desired behavior or algorithm) to the machine;

- a Central Processing Unit (CPU), which executes such program inside the machine, by fetching and invoking instructions, updating relevant registers, and so on.

**Instruction set:** Actions, Events, Conditions A breakdown analysis of MAC protocols reveals that they are well described in terms of three types of elementary building blocks: actions, events and conditions. Actions are commands acting on the radio hardware. In addition to ordinary arithmetic, logic, and memory related operations, dedicated actions implement atomic MAC functions such as transmit a frame, set a timer, build an header field, switch to a different frequency channel, etc.

Actions are not meant to be programmable. As the instruction set of an ordinary CPU, they are provided by the hardware vendor. The set of actions may be extended at will by the device vendor, and complex actions may be considered, so as actions not necessarily restricting to MAC primitives (e.g. perform a PHY encoding/decoding).

**Events** include hardware interrupts such as channel up/down signals, indication of reception of specific frame types, expiration of timers, signals conveyed from the higher layers such as a queued packet, and so on. As in the case of actions, also the list of supported events is a-priori provided by the hardware design.

**Conditions** are boolean expressions evaluated on internal configuration registers. These registers are either explicitly updated by actions, or implicitly updated by events.

Some registers are dedicated to store general MAC layer information (such as channel used, power level, queue length), frame related information (source or destination address, frame size, etc), or more specific MAC parameters (contention window, backoff parameters, etc - used to achieve a more compact protocol description in case of specific MAC designs such as CSMA-based ones).

Actions, events, and registers on which conditions may be set, form the application programming interface exposed to third party programmers. This API is implemented (in principle) oncefor-all, meaning that programs may use such building blocks to compose a desired operation, but have no mean to modify them.

MAC protocols are well suited to be described in terms of Finite State Machines. We chose to rely on the more powerful and expressive model of eXtended Finite State Machines (XFSM). XFSMs are a generalization of the finite state machine model and permit to conveniently control the actions performed by the MAC protocol as a consequence of the occurrence of events and conditions on configuration registers.

An XFSM is formally specified through an abstract 7-tuple (Q,  $\Sigma$ , O, D, F, U,  $\delta$ ): the meaning of such symbolic states and the correspondence with the MAC terminology above introduced is summarized in Table 2.1 (configuration commands being a special case of actions, devised to update registry status). A MAC program is simply a table listing all possible state transition relations. Note that the number and meaning of the set of protocol states is specified by the programmer. By formally describing, per each protocol state, which events and conditions do trigger a state transition, and by associating actions and configuration commands to each state transition, the programmer may access the available hardware primitives, and enforce a desired MAC behavior within the radio hardware. Since the configuration memory is not explicitly represented in the state space, XFSMs allow to model complex protocols with relatively simple transitions and limited state space. For an example, the table programming the legacy 802.11 Distributed Coordination Function MAC protocol is coded in less than 350bytes (see section 3.6), and hence can be transmitted in just a single packet.

| Symbol | XFSM formal notation                                                    | meaning                                   |  |

|--------|-------------------------------------------------------------------------|-------------------------------------------|--|

| Q      | Symbolic states                                                         | MAC protocol states                       |  |

| Σ      | input symbols                                                           | Events                                    |  |

| 0      | Output symbols                                                          | MAC actions                               |  |

| D      | n-dimensional linear space D1 $\times \cdots \times$                    | all possible settings of n configuration  |  |

|        | Dn                                                                      | registers                                 |  |

| F      | Set of enabling functions $f_i$ : D $\longrightarrow$                   | Conditions to be veri fied on the config- |  |

|        | $\{0,1\}$                                                               | uration registers                         |  |

| U      | Set of update functions $U_i : D \longrightarrow D$                     | Configuration commands, update reg-       |  |

|        |                                                                         | isters' content                           |  |

| δ      | Transition relation $\delta : Q \times F \times \Sigma \longrightarrow$ | Target state, actions and configuration   |  |

|        | $Q \times U \times O$                                                   | commands associated to each transi-       |  |

|        |                                                                         | tion                                      |  |

Table 2.1: MAC programs expressed as Extensible Finite State Machines.

#### 2.3.1 WMP architecture

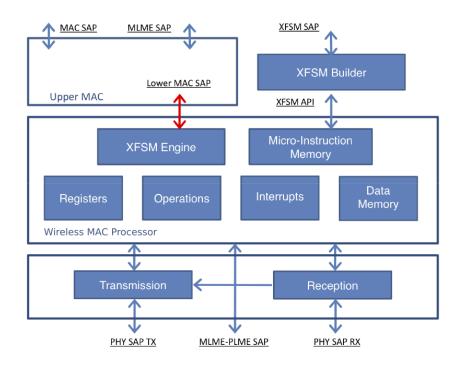

The wireless MAC processor has been conceived as a CPU specialized for handling hardware/PHY events and actions by executing Extended Finite State Machines (XFSMs). The internal architecture of the WMP includes five main components:

- MAC-Engine: an execution engine, running the provided XFSMs;

- A memory block including both data and program memory space;

- An interruption block passing the signals coming from the hardware to the execution engine;

- Application programming interface (API) : a set of operations which can be invoked by the execution engine, which include logic, arithmetic and flow control operations plus specialized MAC operations;

- A set of registers for saving system state parameters.

We discuss every component present in the WMP architecture in the chapters 3.

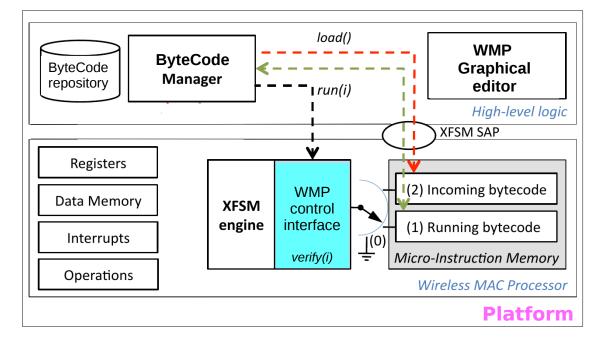

#### 2.3.2 WMP development tool

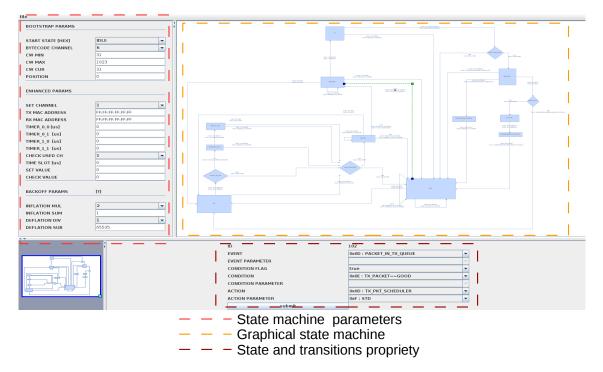

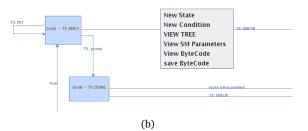

To avoid writing MAC programs in the above described machine language, we have developed an XFSM builder which includes a graphic XFSM editor developed in java language for composing MAC program, and a "Byte-Code compiler" which translates and XFSM graphical representation into the machine MAC program, a language understandable by the firmware's MAC engine. The Byte-Code can be loaded on the memory chipset by using a specific tool named Byte-Code-Manager that also performed a chipset debug tools. Loading a new Byte-Code on the chipset allows changing on-the-fly the card behavior without any recompiling operation. All these element belong to developing tools, in the specific it include:

- **WMP-Editor**, a graphical tool, working as an editor for composing a MAC program in terms of a graphical representation of state transitions and state labels;

- **Translate tool**, able to map the graphical representation into a textual transition table or Byte-Code;

- Byte-Code-Manager able to load, run, and verify the Byte-Code in the WMP platform.

- **Debug tools**, is part of Byte-Code-Manager and permit a useful debug.

The combination of the MAC-Engine, graphical editor, translate tool, Byte-Code-Manager is a complete and cheap tool-chain that allows developing and testing a new MAC scheme in a very simple, robust and quick way over an ultra-cheap platform. We have defined several model of MAC protocol, from common IEEE 802.11 DCF (**complaint with the IEEE standard**) to TDMA MAC protocol and multi channel protocol.

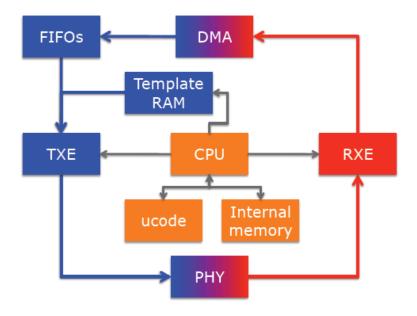

#### 2.3.3 WMP implementation on wireless card overview

In this section we present an overview of the wireless card Broadcom "AIRFORCE 54G" in terms of hardware specified, we use this type of cards to implement the WMP platform. This 802.11g Wireless LAN PCI Card works with both IEEE 802.11b and IEEE 802.11g products. This card uses the Broadcom chipset Broadcom BCM94318KFBG and BCM94311KFBG, both cards are show in the figure 2.2. The BCM43xx is the third generation of Broadcom's single-chip wireless LAN solutions, which combine 2.4 GHz radio, 802.11a/g baseband processor, medium access controller (MAC) and other radio components onto a single chip. The cards are compatible with the linux kernel, and use the b43 driver, this driver is result of a active project, constantly updated. In this overview we present the main element on the card, while we refer more detail on the WMP implementation on this wireless card in the chapter 6, the main element present in the wireless card are:

- 1. Broadcom CPU: This is a 8 MHz CPU with 64 registers;

- 2. **Shared memory**: This memory space of 4 KB can be accessed also by the host and can be used for implementing the micro-instruction memory, i.e. the MAC program;

- 3. **Internal code memory**: This 32 KB memory is used for implementing the MAC commands and the MAC engine;

- 4. **Internal registers**: The internal registers keep hardware configuration settings. They can be set by the processor in response to changes in the program, and in the interface;

The Broadcom wireless card has a tools for debugging and compiling the source program code, all program are collect together in a project named b43-tool, all tools can be downloaded ad the address [17], and support different cards. Main tools perform the firmware compiling and the dump of the different memory and registers. The tool to compiling the source code is named b43-asm, other tool b43-fwdum shows the contain of the memory and registers.

Figure 2.2: Broadcom wireless card

# **Chapter 3**

# WMP Architecture

Wireless card architectures have tremendously evolved in the last years in order to transfer to the host processor the functionalities which do not require strict time constraints. While old devices were designed according to a full-MAC approach, where the control of all the MAC functionalities were entirely performed by the card, recent devices exploit an innovative soft-MAC approach, where important MAC primitives are supported by the driver on the host.

Our design starts from the consideration that most modern wireless cards do embed a generalpurpose CPU for supporting the hardware control logic. We propose to push this approach farther, by transforming the card itself in a specialized processor, called Wireless MAC Processor (WMP) [5].

### 3.1 General WMP Architecture

As enlightened in the previous part, commercial 802.11 drivers and chipsets do not currently support the possibility of defining a customized protocol logic for managing the access to the shared medium and the sequence of frame transmissions. Indeed, making the protocol control logic programmable is not an easy task, because this logic cannot be programmed in the card host (due to the time contraints of the access operation) and cannot be supported by a simple configuration interface exposed by the card. In order to support this complex flexibility requirement, we envision a solution based on the introduction of wireless-processors exposing a standardized instruction set, and acting as a mediation layer between the vendor-specific hardware platform (i.e. the PHY layer and the processor implementation) and the upper-MAC functionalities. According to this vision, different medium access control protocols can be programmed through the standardized instruction set, and loaded and executed by the wireless-processor.

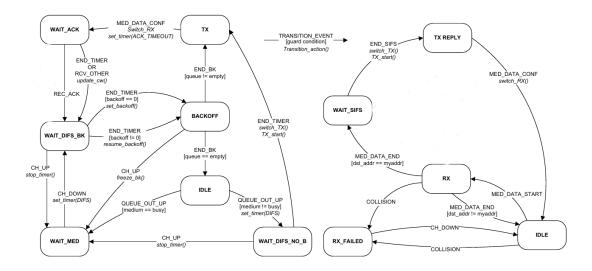

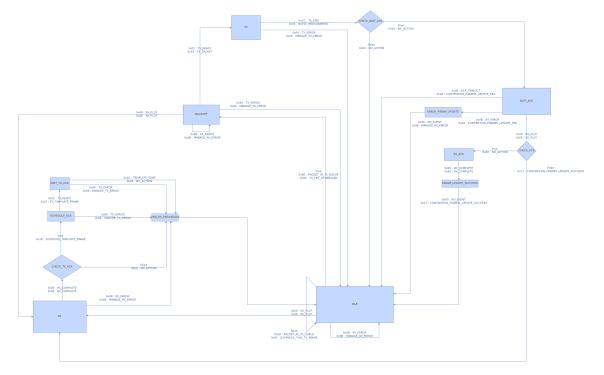

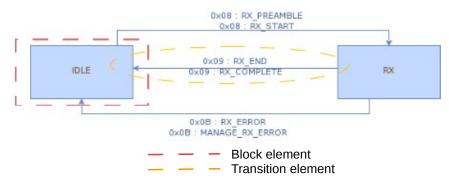

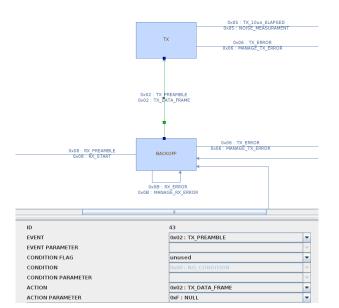

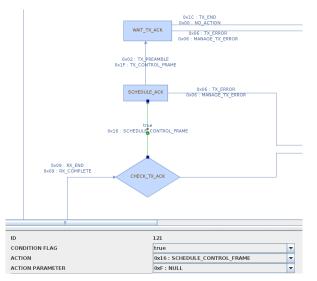

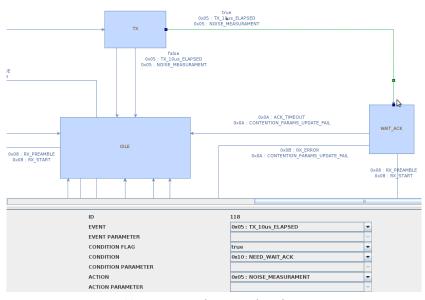

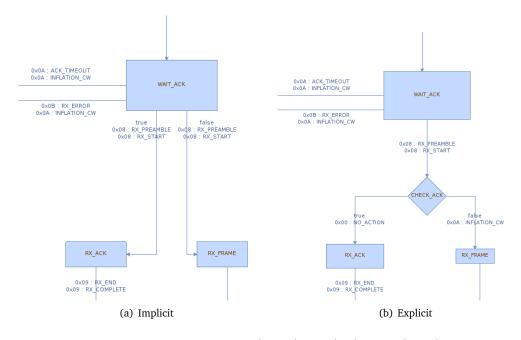

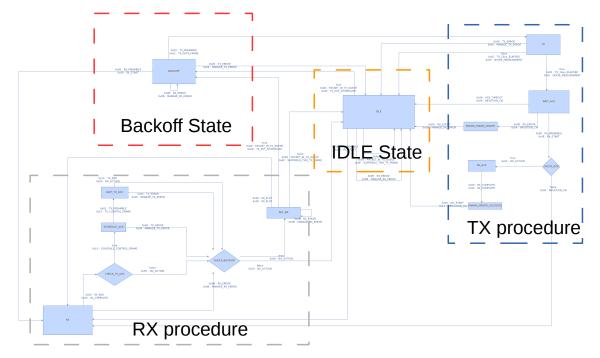

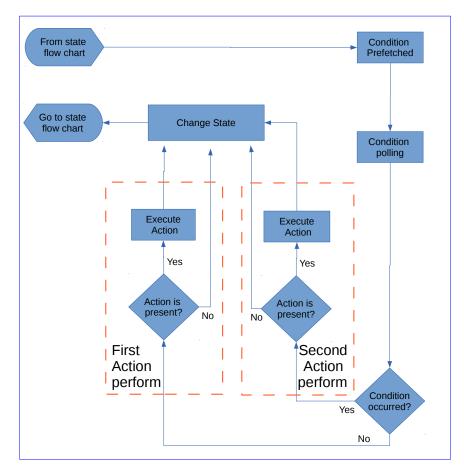

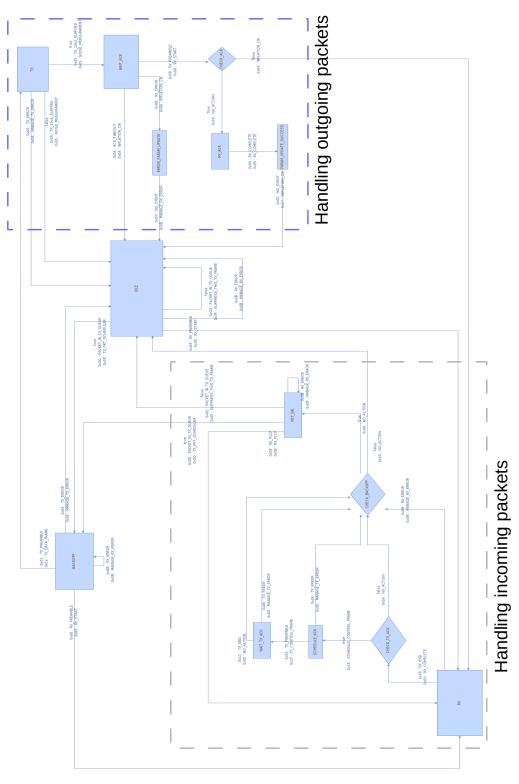

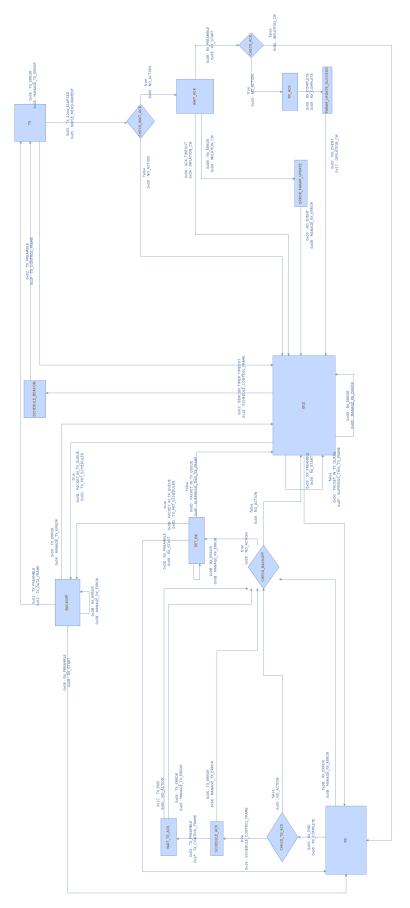

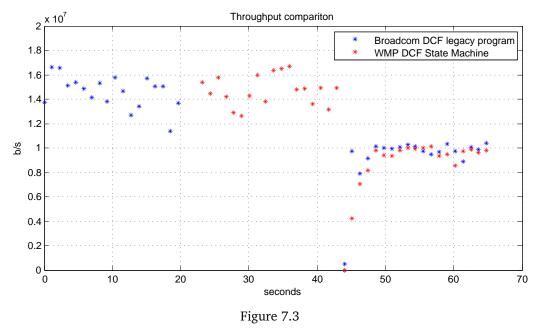

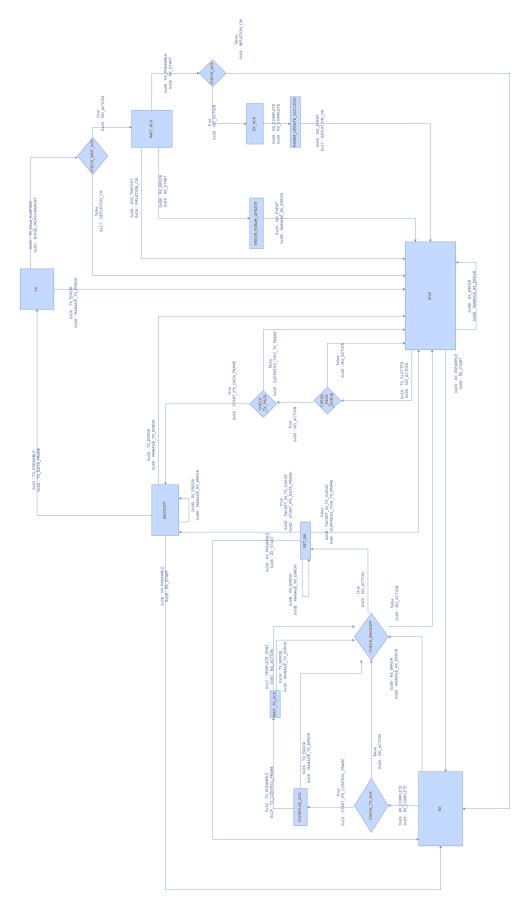

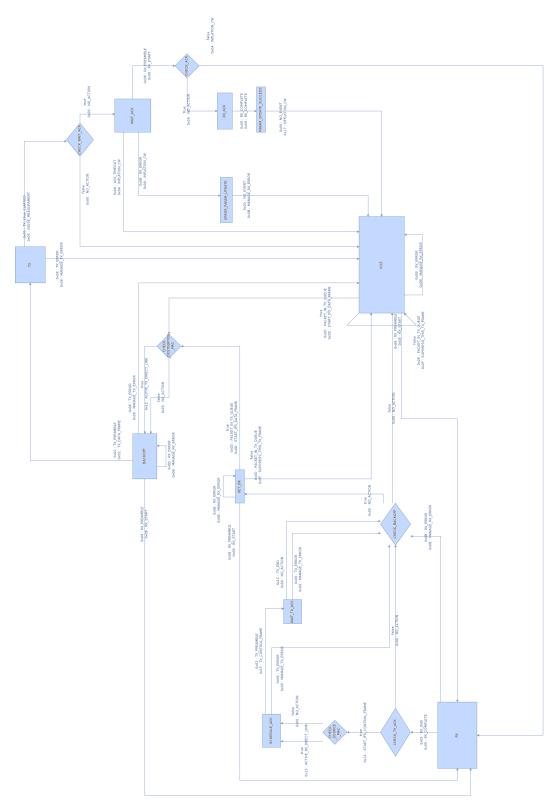

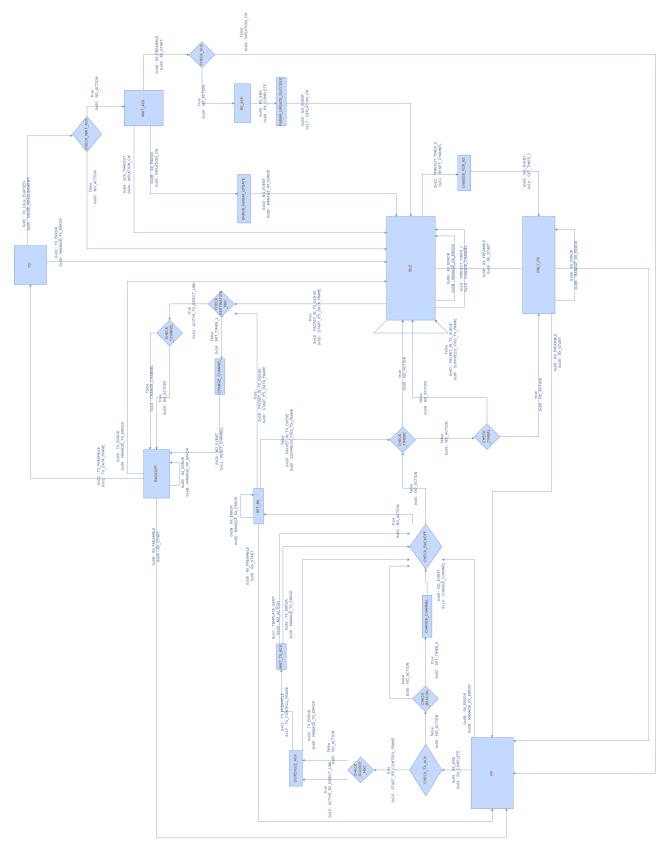

We define a MAC programs as programmable XFSM, rather than as programmable data flows. Our choice is motivated by the observation that data flows are usually more suitable for dynamic signal and data processing, while state machines are more effective for modeling the behavior of sequential control operations [19]. Moreover, the wireless-processor operations are much simpler than the MAC blocks used in [34], thus allowing a higher level of programmability. As an illustrative example, we consider the definition of the Distributed Coordination Function (DCF) [43], in the basic access case. Figures 3.1 shows (in normal style) the state machines of the two sub-systems in which the DCF behavior has been decomposed: a **transmitter sub-system** and a **receiver sub-system**. The state machine is depicted by specifying the state labels, the transition events, the guard conditions (in the square brackets), and the transition actions (in italic style). The figure shows that a MAC protocol is easy defined through a XFSM, and for this example we use events, conditions and action extract through a process of abstraction, in the next section we study in deep the API that can be implemented follow the logic of the hardware.

For sake of presentation completeness, we summarize the transmitter sub-system behavior. Starting from the IDLE state, as a new frame is enqueued in the hardware buffer (QUEUE\_OUT\_UP event) the transition to the state WAIT\_MED or WAIT\_DIFS\_NO\_BK is performed according to the state of the medium. If the medium is idle, a timer equal to the DIFS interval is set and a transmission is started (i.e. the trans-receiver is switched to the transmission mode and the system moves to the TX state) as the timer expires (END\_TIMER event). If the medium is busy, the system remains in the state WAIT\_MED until the event representing the end of the medium activity (CH\_DOWN event) is registered. At this point, the system sets a timer equal to the DIFS interval and transits to the state WAIT\_DIFS\_BK. At the timer expiration, a backoff countdown has

to be performed. Therefore, the system runs a sequence of actions according to the verification of a condition on the residual backoff: if there is not a residual backoff time, a new backoff timer is set-up, otherwise the frozen backoff timer is resumed.

A transition to the BACKOFF state is then performed. If the backoff timer expires, the system can transit to the TX state, but if the medium is revealed as busy during the timer expiration (CH\_UP event), the timer is frozen and the state comes back to the WAIT\_MED state. From the TX state, the event signalling the end of the frame transmission (MED\_DATA\_CONF event) triggers the switch of the tran-receiver to the reception mode and the transition to the WAIT\_ACK state. Finally, at the end of an acknowledgement reception (RCV\_ACK event), the post-backoff is performed by transiting again to the WAIT\_DIFS\_BK state. A similar description can be detailed for the receiver sub-system. Note that both the state machines can be defined by using the same sets E, A, and C.

Figure 3.1: MAC Programs

The WMP is devised to specifically handle hardware/PHY events and schedule actions on the hardware/PHY card resources, thus leaving the MAC protocol developer with the much simpler task of describing when and under which events and/or conditions such actions should occur. In other words, similarly to other processors specialized for handling digital signals (DSPs) or graphical images (GPUs), we introduce a processor specialized for handling MAC operations.

The wireless MAC processor has been conceived as a CPU specialized for handling hardware/-PHY events and actions by executing Extended Finite State Machines (XFSMs). We chose to abstract the definition of the medium access control logic in terms of state machine because they are very effective in modelling the behavior of sequential control operations, and most MAC protocols are formally described in terms of state machines [5].

Figure 3.2 shows the internal architecture of the WMP, which includes five main components:

- MAC-Engine : an execution engine, running the provided XFSMs;

- API : a set of operations which can be invoked by the execution engine, which include logic, arithmetic and flow control operations plus specialized MAC operations;

- A memory block including both data and program memory space;

- An interrupts block passing the signals coming from the hardware to the execution engine;

- A set of registers for saving system state parameters.

- Byte-Code-Manager able to load and run the bytecode in the WMP platform.

Memory block, interrupts block and registers are physical elements able to save date and interact with the hardware, instead other element are main element and will be discuss in the next section of this chapter.

The core of the wireless-processor architecture is represented by an Extended Finite State Machine (XFSM) Execution Engine [19]. This block represents a micro-code executor, able to run a programmable finite state machine loaded in the instruction memory. Formally, a state machine is specified by a list of states and transitions. In a state machine, a transition is given by:

Figure 3.2: Internal architecture of the Wireless MAC processor

- a source state, from which the state machine starts its operations;

- a trigger event, such as a signal or a timer expiration;

- an optional guard condition, to be evaluated after the trigger event (which can be true or false);

- an action, representing an atomic program code, which can also create, move or destroy data objects;

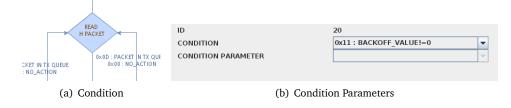

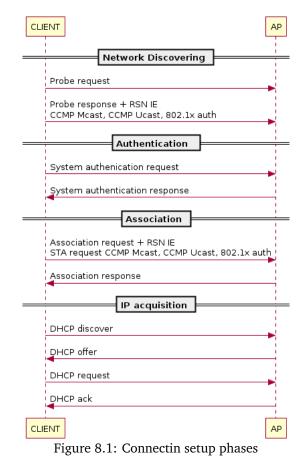

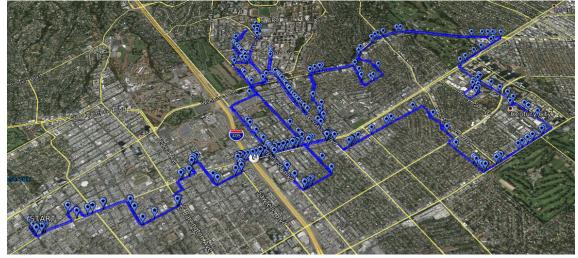

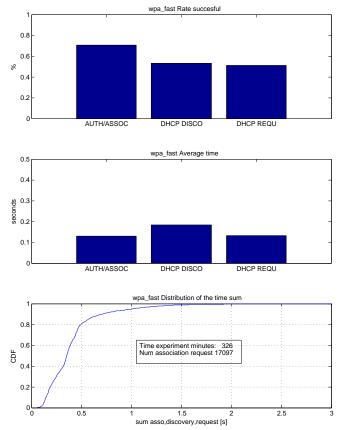

- a target state, in which the state machine enters at the end of the action.